Dynamic random access memory unit and its array, and Method of making the same

A dynamic random access and memory cell technology, applied in semiconductor/solid-state device manufacturing, electrical components, transistors, etc., can solve problems such as increasing the surface area of capacitors, and achieve the effect of quality improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

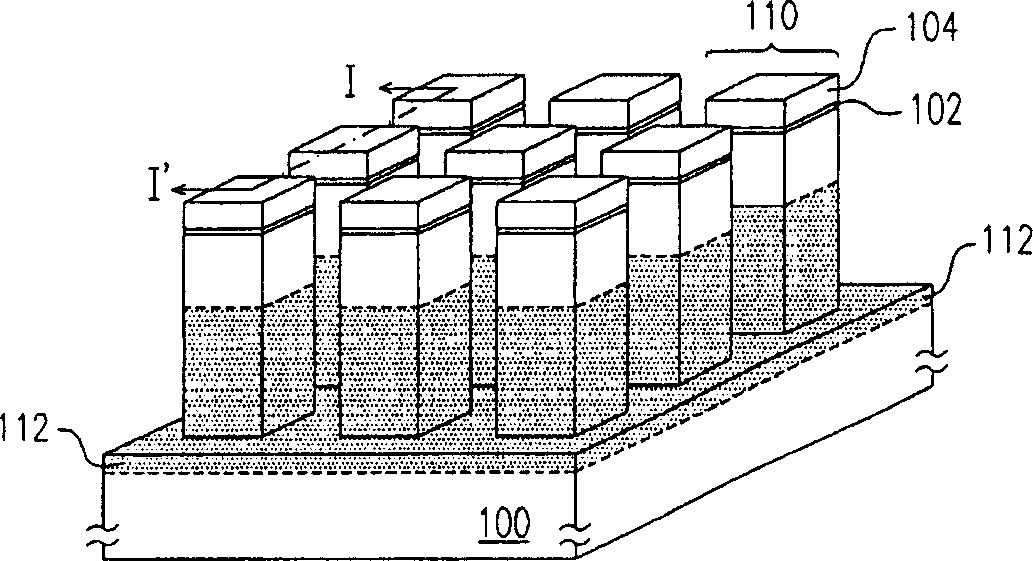

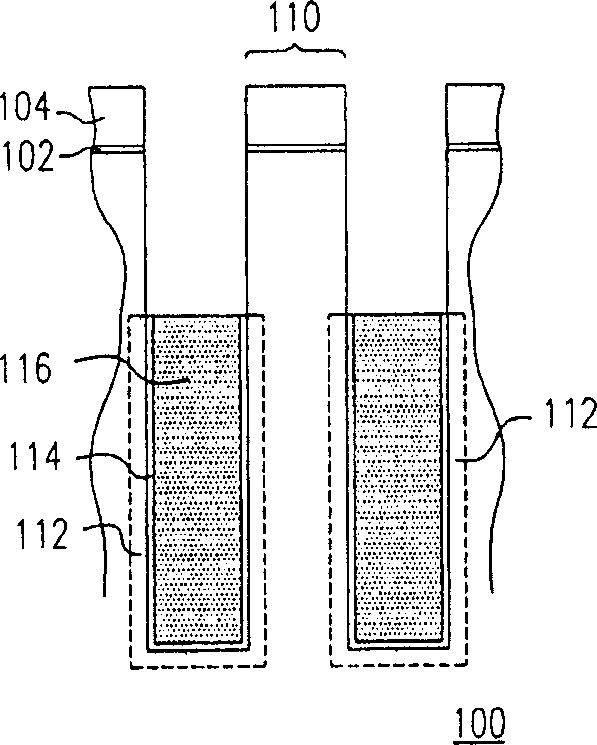

[0030] figure 1 perspective view clearly showing the dynamic random access memory array, Figure 2 to Figure 11 , Figure 13 to Figure 15 as well as Figure 18 (a) is along the figure 1 The cross-sectional schematic diagram of the I-I' line in Figure 18 (b) is another schematic sectional view, and Figure 12 , Figure 16 and Figure 17 All are top views.

[0031] More specifically, Figure 1 to Figure 7 Shown is a schematic of the fabrication process for forming capacitors for dynamic random access memory arrays, Figure 8 to Figure 14 Illustrated is a schematic of the fabrication flow of transistors forming a dynamic random access memory array, and Figure 15 to Figure 18 Shown are subsequent steps, including bit line and word line manufacturing methods.

[0032]

[0033] First, please refer to figure 1 , providing a semiconductor substrate 100 made of, for example, lightly doped P-type single crystal silicon, and forming a pad oxide layer 102 and a patterned...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com