Semiconductor device having trench isolation

A trench isolation, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., can solve the problems of deterioration of the reliability of the gate insulating layer, difficulty in manufacturing high-performance transistors or flash memory, etc., to prevent reliability. worsening effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

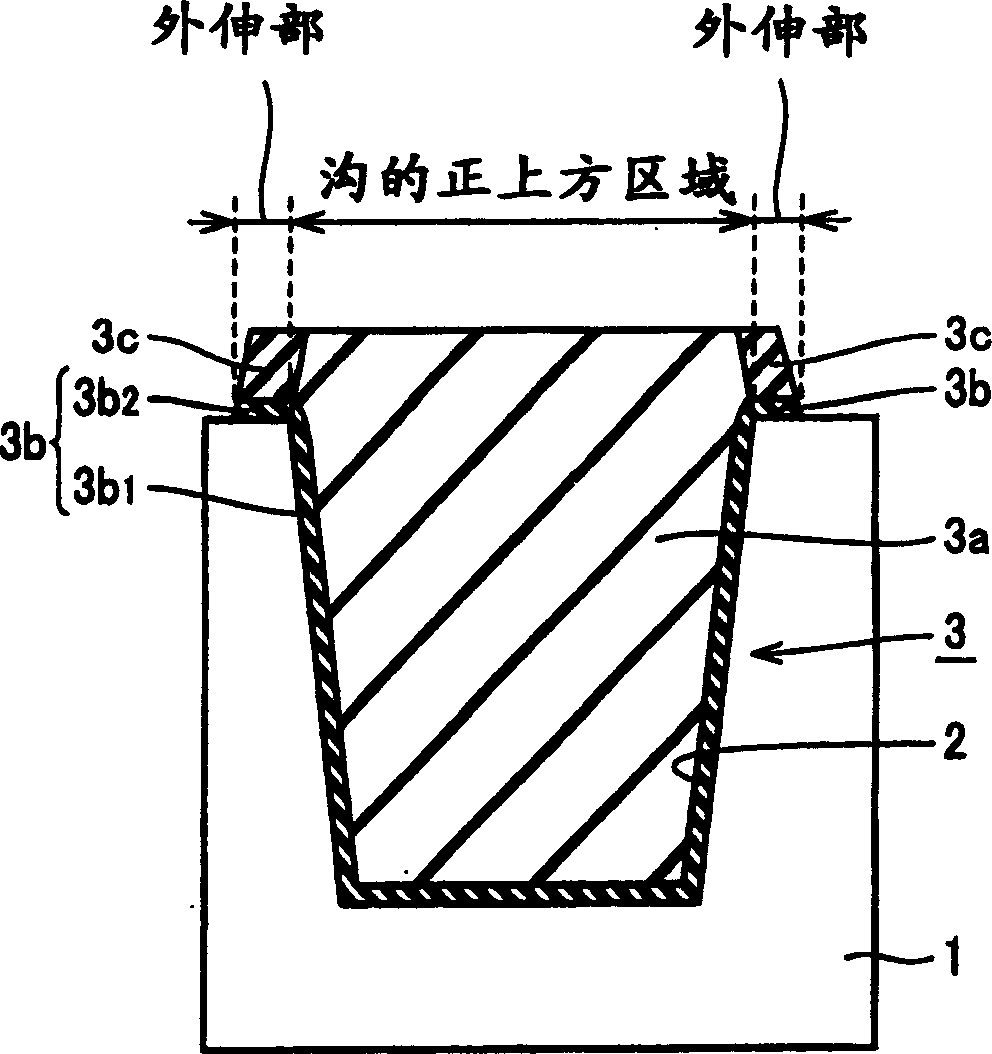

[0031] Such as figure 1 As shown, the semiconductor device of this embodiment is provided with a trench isolation portion for electrically isolating a semiconductor element from other semiconductor elements. The trench isolation portion includes, for example, a trench 2 for trench isolation formed on the surface of a semiconductor substrate 1 made of silicon, and a buried insulating layer 3 filling the trench 2 . The buried insulating layer 3 fills the trench 2 and protrudes from the surface of the semiconductor substrate 1 . The protruding portion has an overhanging portion protruding outward (in a direction parallel to the surface of the semiconductor substrate) from a region immediately above the groove 2 on the surface of the semiconductor substrate 1 . The overhanging portion has a structure in which at least two insulating layers are laminated. Furthermore, the entire upper surface of the buried insulating layer 3 is located above the surface of the semiconductor subst...

Embodiment 2

[0037] refer to figure 1 , in the semiconductor device of this embodiment, the insulating layer 3b constituting the overhang 2 and insulating layer 3c are made of different silicon oxide films. insulating layer 3b 2It consists of a silicon oxide film (hereinafter referred to as a thermal oxide film) formed by a thermal oxidation method. The insulating layer 3c is made of a silicon oxide film formed by a method other than thermal oxidation, for example, a silicon oxide film formed by HDP (High Density Plasma: High Density Plasma) (hereinafter referred to as an HDP oxide film), or a silicon oxide film formed by TEOS ( Tetra Ethyl Ortho Silicate: a silicon oxide film formed of Tetra Ethyl Ortho Silicate (hereinafter referred to as a TEOS oxide film) and the like. Therefore, the insulating layer 3b and the insulating layer 3c have mutually different film qualities.

[0038] In addition, the insulating layer 3a is made of, for example, an HDP oxide film, and the insulating laye...

Embodiment 3

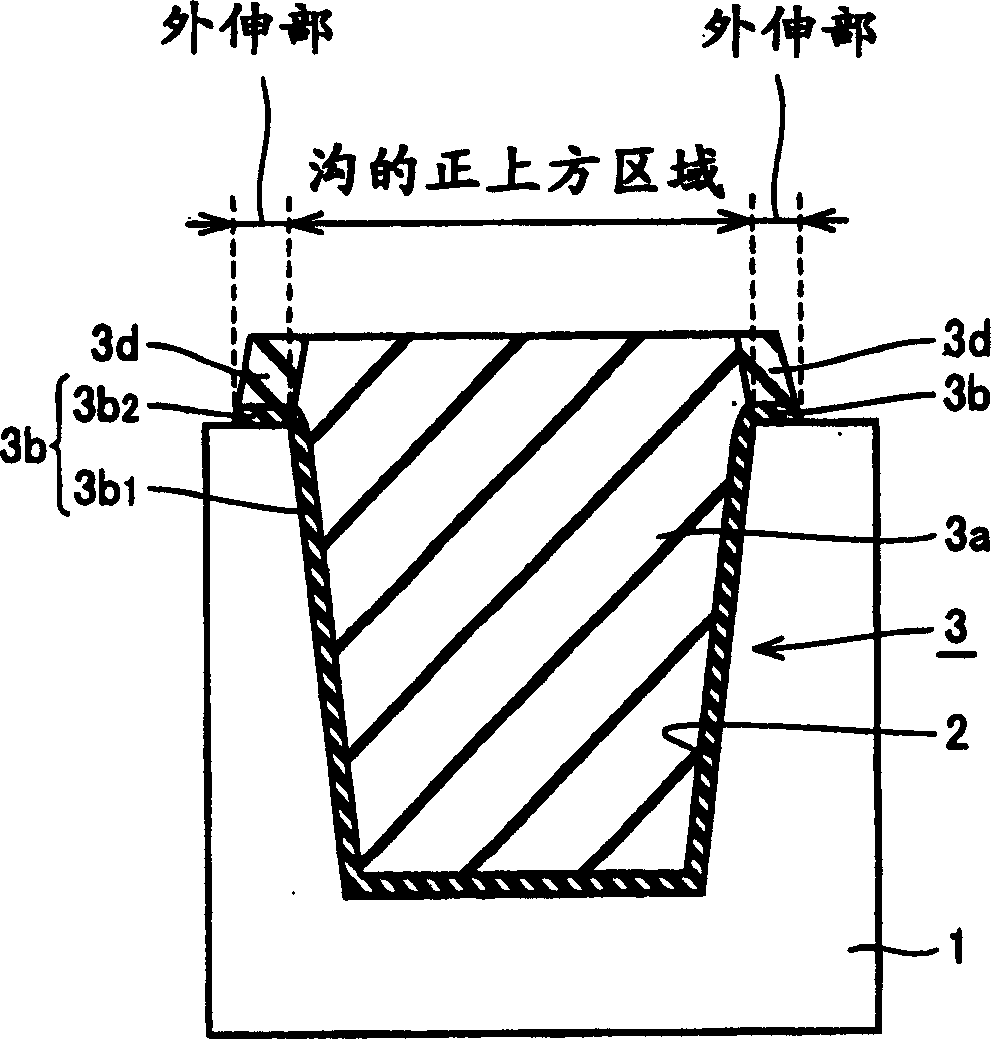

[0044] refer to figure 2 , compared with the structure of Embodiment 2, the difference of the structure of this embodiment is that the insulating layer 3b constituting the overhang of the buried insulating layer 3 2 and the insulating layer 3d are made of different materials from each other. insulating layer 3b 2 It is made of a thermal oxide film, and the insulating layer 3d is made of a silicon nitride film.

[0045] Since the insulating layer 3a is made of a silicon oxide film, the insulating layer 3a and the insulating layer 3d are made of different materials.

[0046] In addition, the structure other than that in this embodiment is substantially the same as that of the above-mentioned embodiment 2, and therefore the same components are denoted by the same reference numerals, and description thereof will be omitted.

[0047] According to this embodiment, since the insulating layer 3d is made of a silicon nitride film, the insulating layer 3b is removed by wet etching w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com