Exposure process for different levels

An exposure method and layered technology, applied in microlithography exposure equipment, photolithography exposure devices, optics, etc., can solve problems such as inapplicability, difficulty in evaluating the pros and cons of integrated circuits, and high manufacturing costs of photomasks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

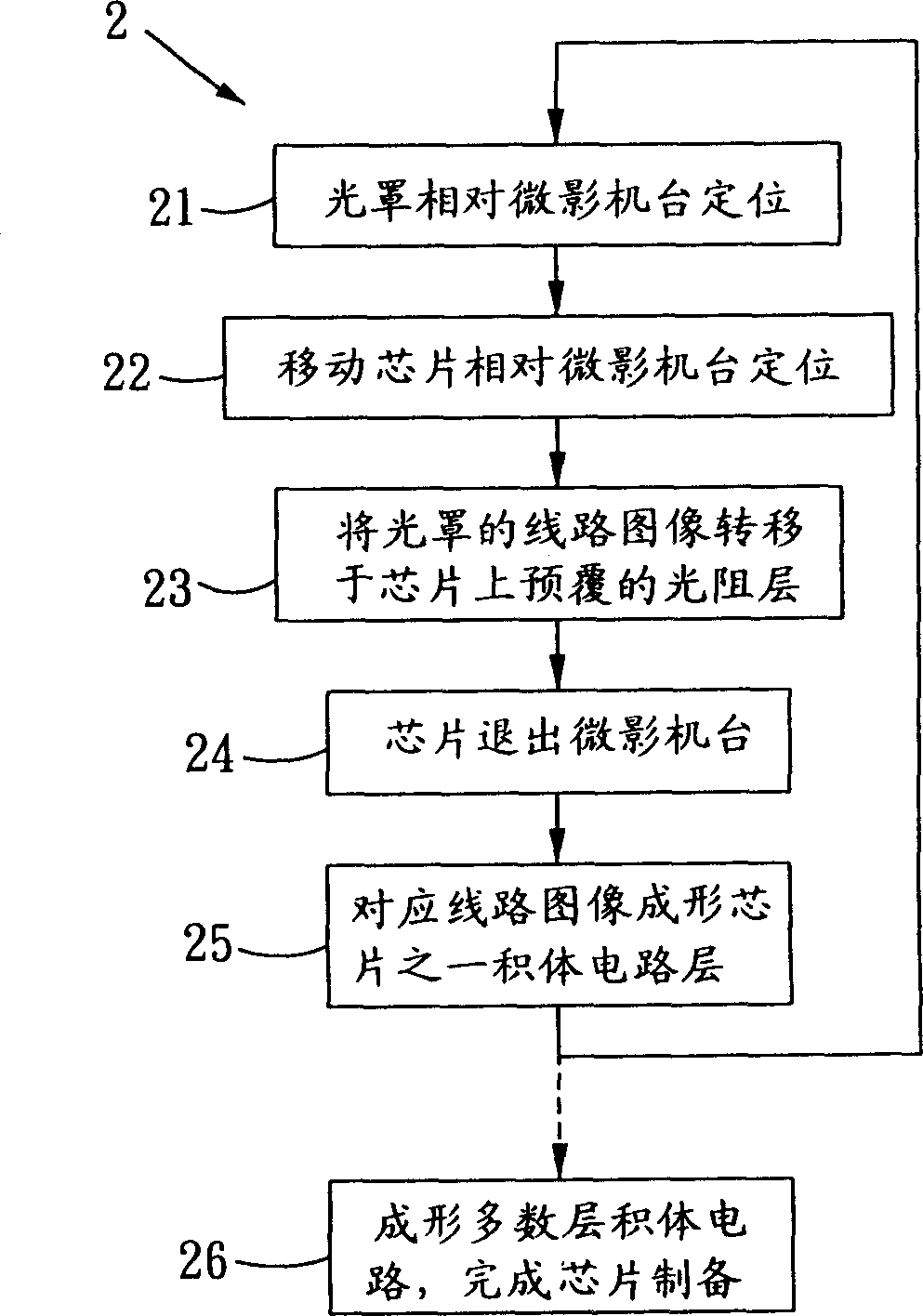

[0055] The different levels of exposure method 3 of the present invention is applicable to the manufacture of many chips in small batches, and a lithography machine is used to perform multi-level exposure on the chips. Each chip has a plurality of integrated circuit layers. In this example, a six-layer integrated circuit will be formed. layer as an example.

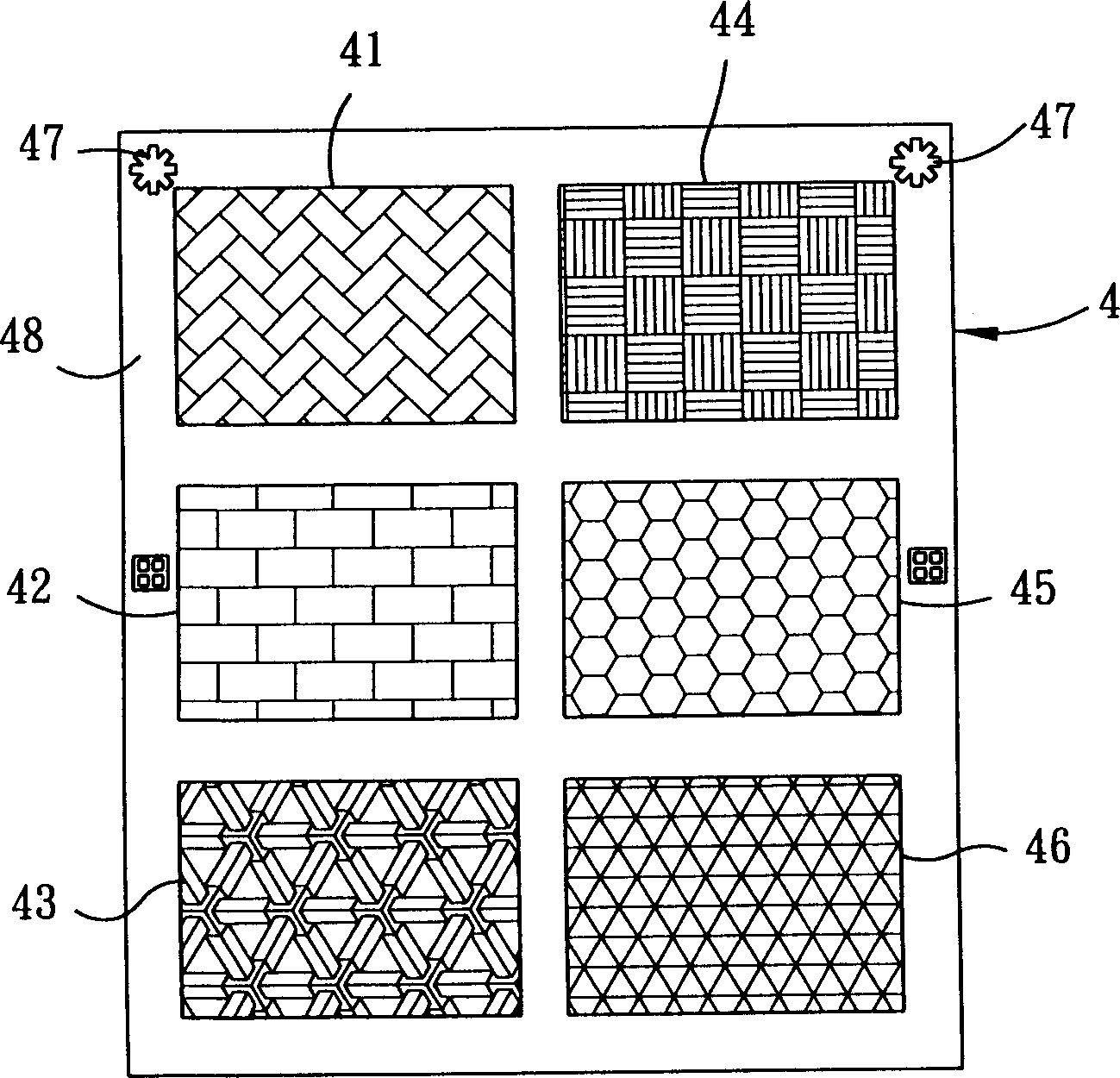

[0056] like image 3 As shown, the photomask 4 used in the present invention can be a binary photomask, or a phase shift photomask, including six different line images 41, 42, 43, 44, 45, 46, and most of them are located at the corners of the four corners. font or rice-shaped positioning mark 47 (in the icon, the rice-shaped character is used as an example), each of the circuit images 41, 42, 43, 44, 45, 46 is designed for each layer of integrated circuits, and these circuit images 41, 42, 43, 44, 45, 46 are also plated with a layer of chromium film with a thickness of about several hundred Å to form a non-light-transmit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com