High radiation miniature package for semiconductor chip

A technology of high heat dissipation and packaging, which is applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., and can solve the problems that the volume of packages cannot be effectively reduced

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

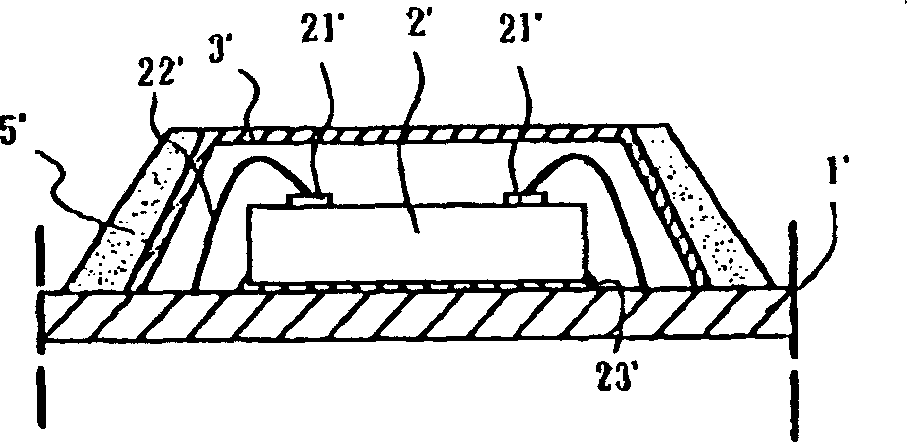

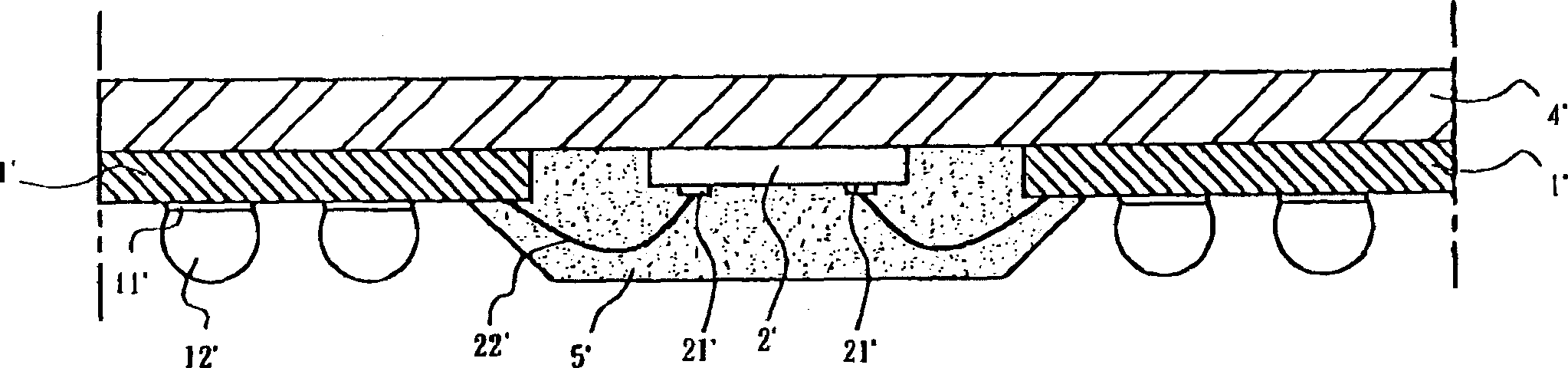

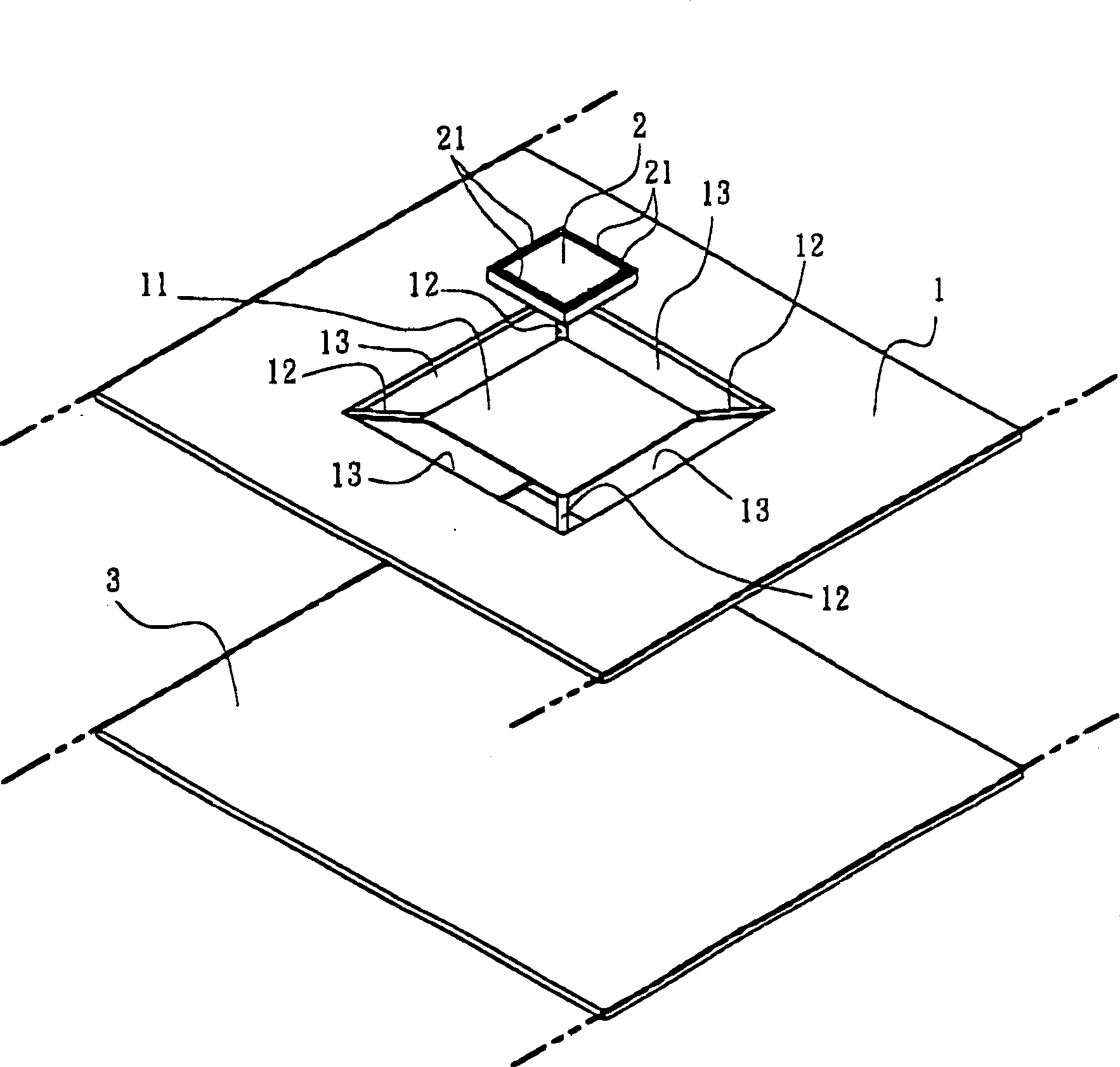

[0017] See first image 3 , Figure 4 As shown, the high heat dissipation tiny package body of the semiconductor chip of the present invention comprises:

[0018] A lead frame 1, the lead frame 1 produces a platform of a recessed chip holder 11 by an etching process, and hollow hollow slots 13 are set around the chip holder 11, leaving only a few supporting strips 12 connected to the lead frame main body ;

[0019] A substrate 3, the substrate 3 can be applied to the production of high-density circuits to meet the requirements of high pin count, the substrate 3 is attached to the bottom of the lead frame 1, and the substrate 3 is provided with high-density circuits and a large number of foot pads 31 and solder balls 32, and make the pads 31 in the hollow slot 13 relative to the lead frame 1, so as to join the gold wires 22;

[0020] A chip 2, the chip 2 is positively bonded to the chip holder 11 of the lead frame 1 with the bonding agent 23, and the gold wire 22 is placed o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com