Method for mfg. semiconductor substrate

A semiconductor and substrate technology, applied in the field of semiconductor substrates, can solve the problem that the SiGe layer is not enough for commercial device applications

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

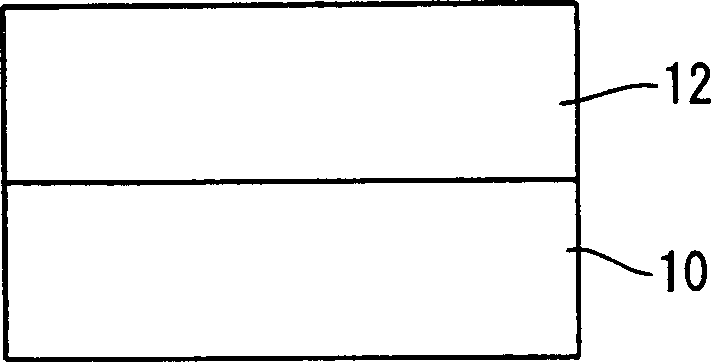

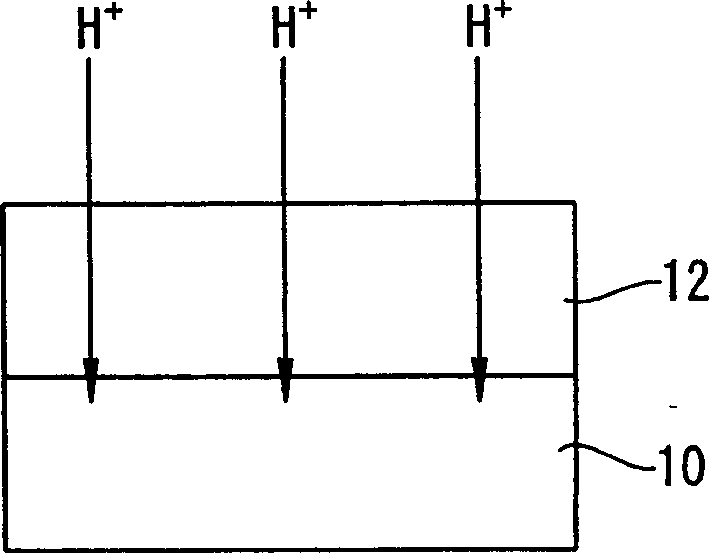

Image

Examples

Embodiment approach

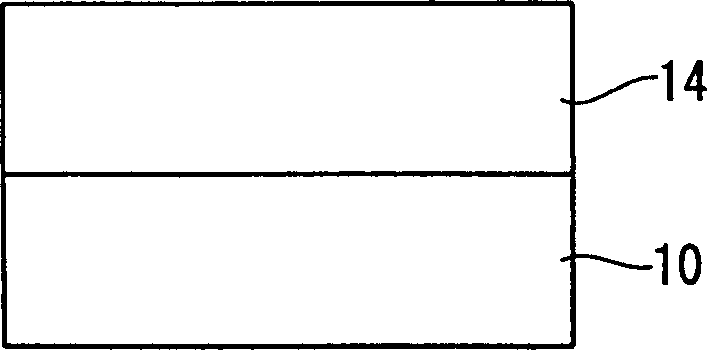

[0045] The method of the present invention can be modified by: growing SiGe layer over 300nm thickness with graded Ge distribution with surface Ge content over 22% + H-II + RTA (to relax SiGe layer stress) + tension table - silicon cap / via . This does not require the deposition of a second SiGe layer.

[0046] Another embodiment of the method of the present invention includes growing the first SiGe layer using either constant or graded Ge distribution + H-II + RTA (to relax the stress of the SiGe layer) + surface Ge content exceeding 22% or constant or graded Ge distribution of the second SiGe layer + tension table - silicon caps / vias. In this embodiment of the inventive method, the thickness of the entire SiGe layer should be 300 nm or higher.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com