Multi-valued memory

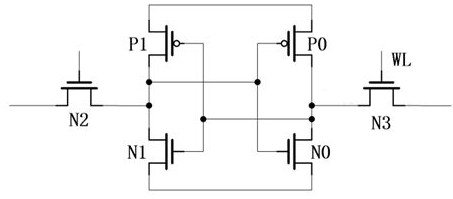

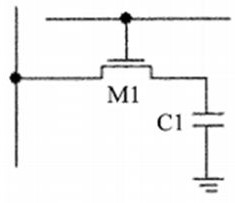

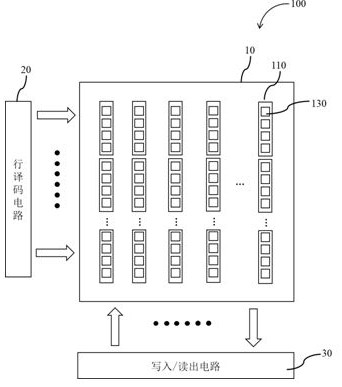

A memory and charge storage technology, applied in semiconductor devices, electro-solid devices, climate sustainability, etc., can solve the problems of complex logic circuits, shortened refresh time, chip surface damage, etc., achieve simple circuit architecture, and improve integration density. , The effect of reducing the circuit design area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] In the description below, many specific details are explained to fully understand the invention. However, the present invention can be implemented in many other ways that are different from this description. Technical personnel in the art can do similar promotion without violation of the connotation of the invention. Therefore, the invention is not restricted by the specific implementation of the following publicity.

[0044] Secondly, the present invention uses a schematic diagram for detailed description. When detailing the examples of the present invention, in order to facilitate the explanation, the schematic diagram is only an instance, and it should not limit the scope of the protection of the invention.

[0045] In order to make the above invention's above, characteristics, and advantages of the present invention more obvious, the following combined with the attachment of the attachment to describe the method of the present invention in detail.

[0046] The invention...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com