Chip packaging structure

A chip packaging structure and chip technology, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problems of chip temperature rise, size limitation, inapplicability, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

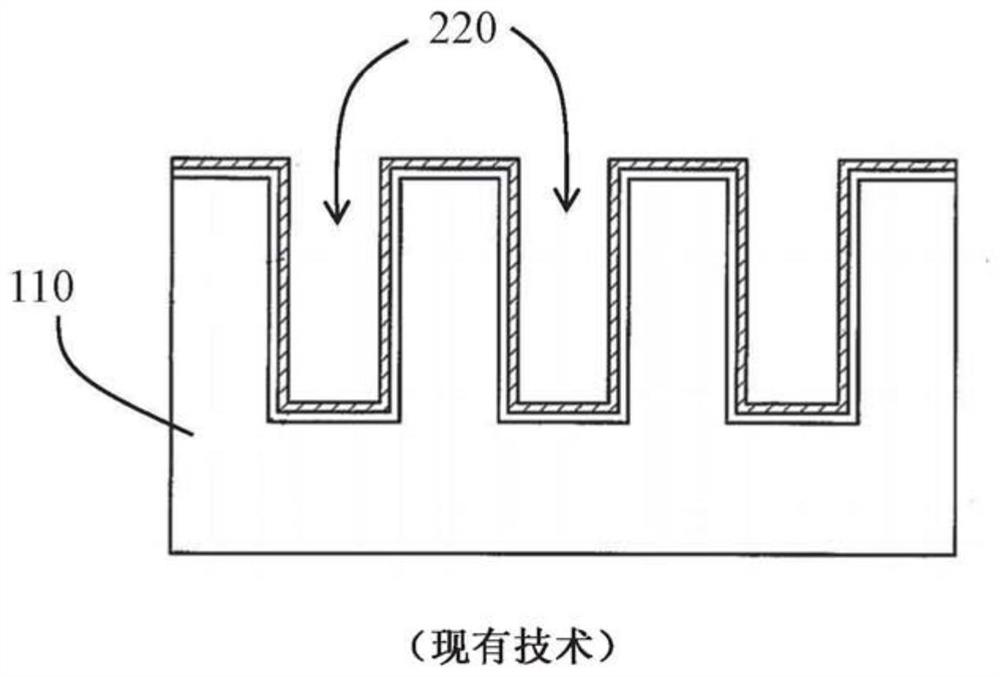

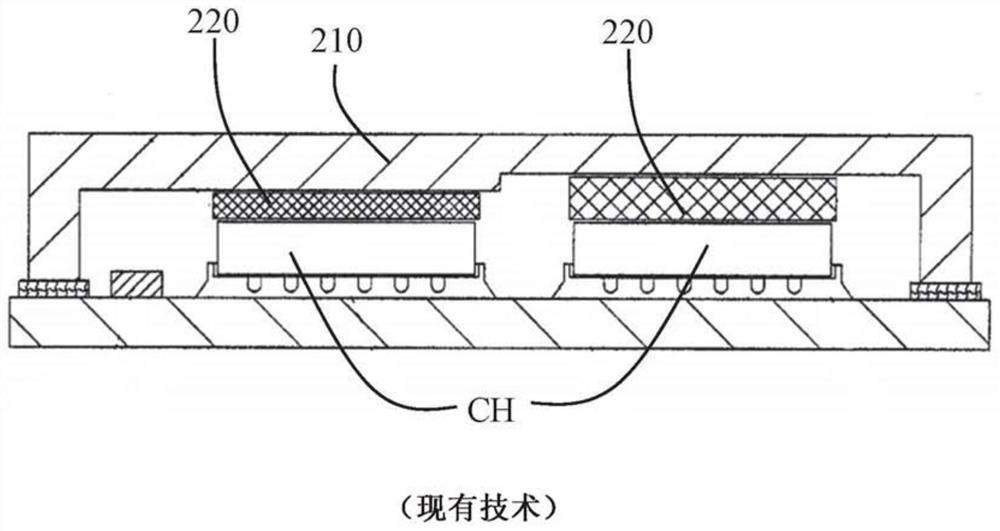

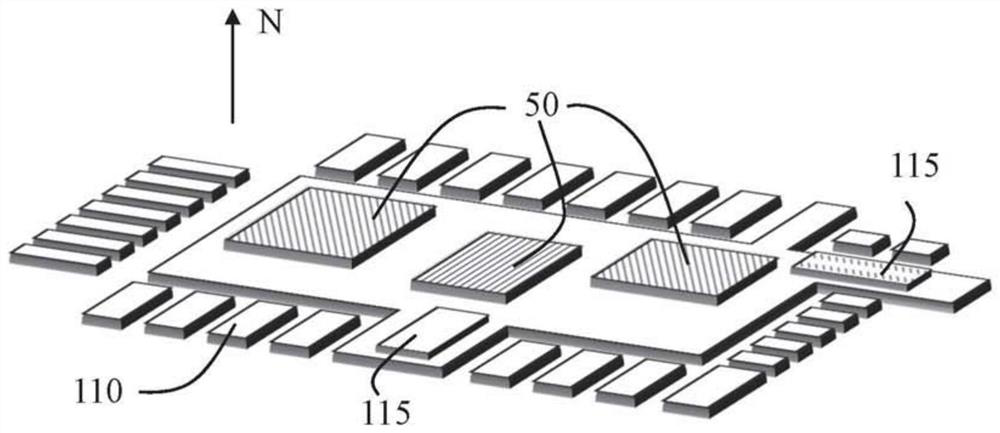

[0038] The drawings in the present invention are schematic, mainly intended to show the relationship between the components of the various elements, and the shapes and sizes are not drawn according to scale.

[0039] In order to provide high-efficiency heat dissipation function, according to one point of view, refer to Figure 3A and Figure 3B , Figure 3A It is a schematic diagram of the state before encapsulation, Figure 3B Schematic diagram of the state after encapsulation of the encapsulation material. Among them, the present invention provides a chip package structure 10, which includes: at least one semiconductor chip 50, which has a signal processing function, and optionally has at least one copper pillar 55 (Copper pillar). The number of copper pillars 55 of the present invention is not limited to this number, and it can be determined according to the needs of heat dissipation, such as no copper pillars, one or more copper pillars; a substrate 110, and the semicon...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com