General hardware accelerator system platform oriented to YOLO algorithm and capable of being rapidly deployed

A hardware accelerator and system platform technology, applied in neural learning methods, biological neural network models, neural architectures, etc., can solve problems such as high deployment difficulty, high power consumption, and general-purpose processor CPUs that cannot meet high-performance requirements. The effect of high complexity and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The present invention will be further described in detail below with reference to the accompanying drawings.

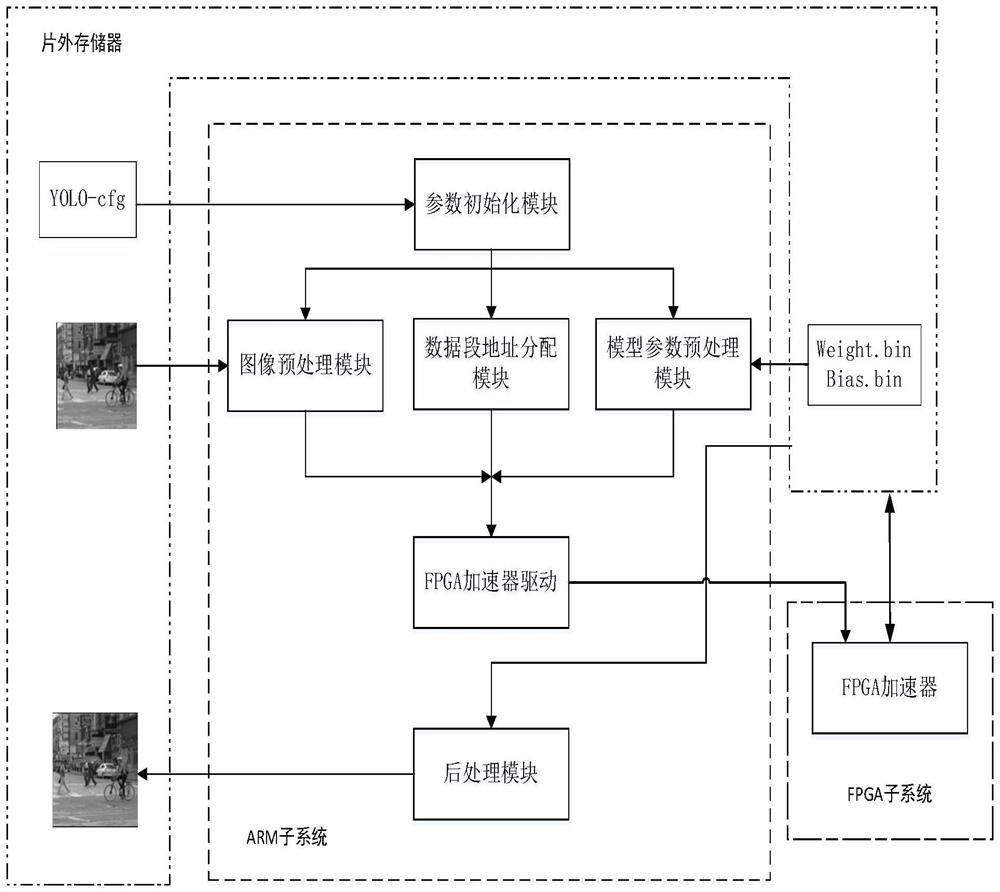

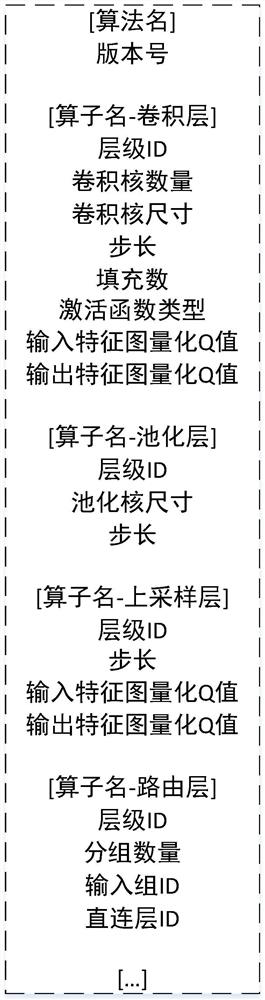

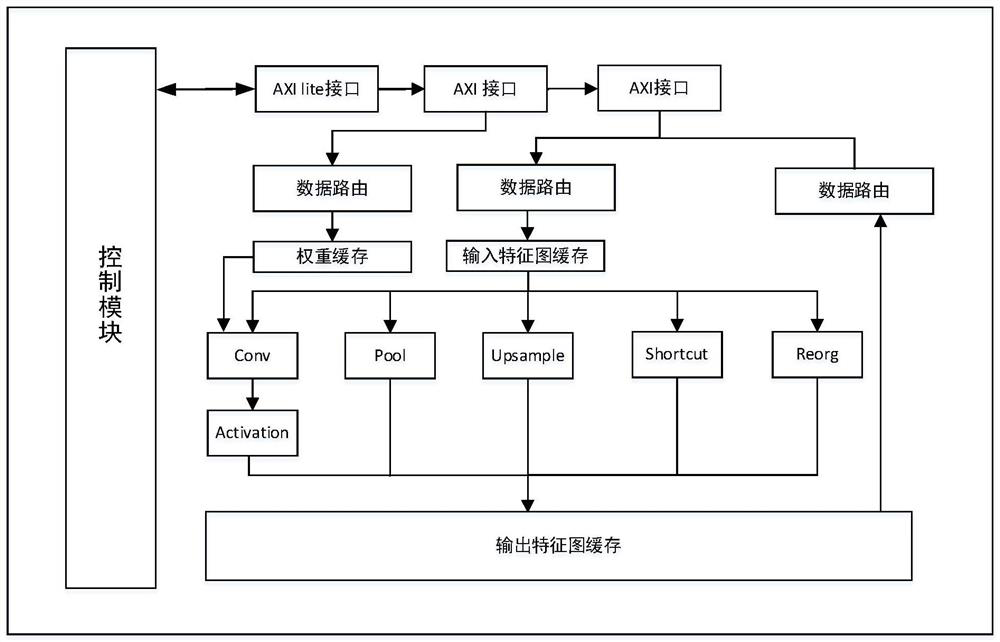

[0014] like figure 1 Shown is a schematic diagram of the system platform of the present invention, which is mainly composed of an ARM subsystem, an FPGA subsystem and an off-chip memory. When the system starts, the parameter initialization module in the ARM subsystem reads the configuration file of the algorithm, completes the initialization of the structure variables of the drive parameters, and the configuration file is written in a certain format, such as figure 2 As shown, it includes the YOLO algorithm version, the operator type of each layer of the model, the size and number of convolution kernels, the step size, the activation function type, the quantized Q value of the input and output feature maps, the level ID and the number of routing layers, and the input group ID, directly connected layer ID algorithm information, the driving structure types are ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com