Low-resource-consumption DICE trigger design method based on commercial technology

A technology of resource consumption and design method, applied in pulse generation, electrical components, generation of electrical pulses, etc., can solve the problems of large layout design area and high overhead, and achieve the effect of improving reliability and strong pertinence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

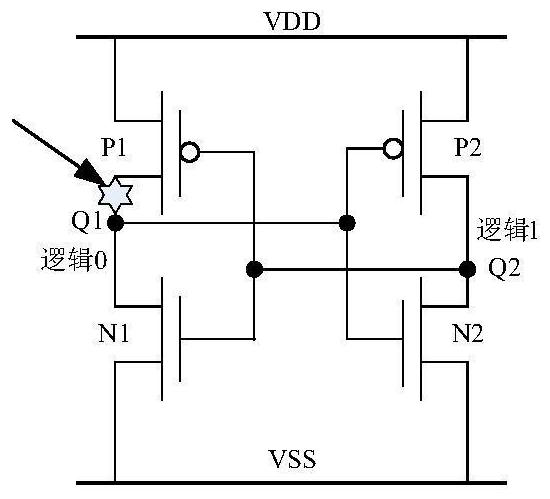

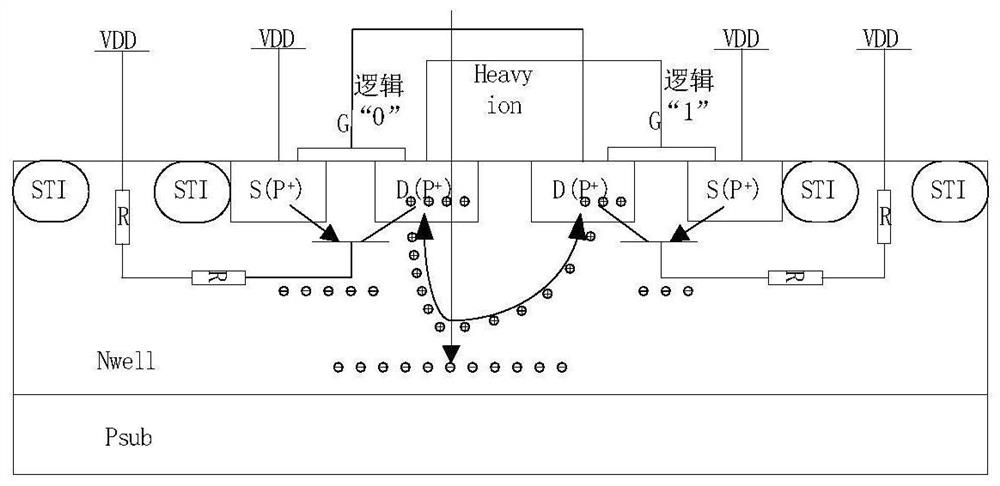

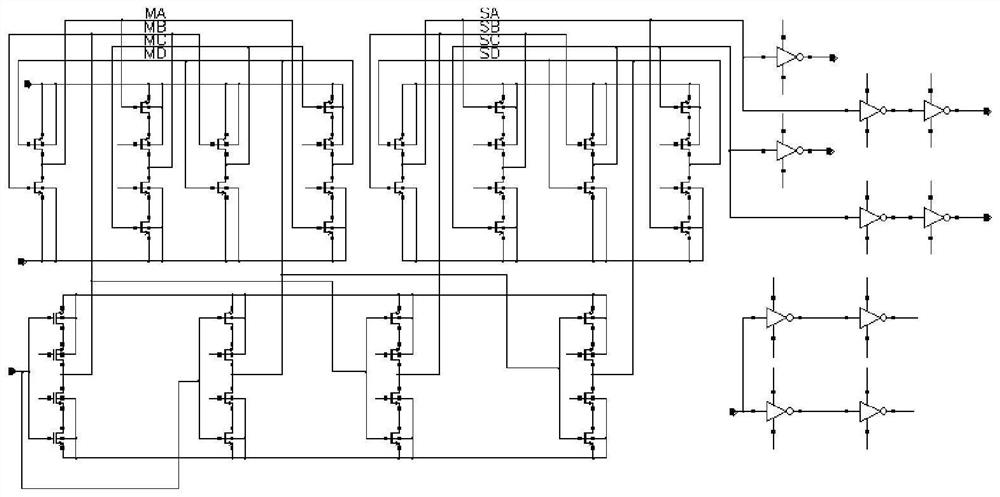

[0026] In order to improve the SEU protection capability of ASICs developed using 65nm anti-adding libraries, and minimize the area and performance overhead, a low-resource-consumption DICE flip-flop design method based on commercial processes is proposed, without affecting the chip design process. Under such circumstances, starting from the SEU occurrence mechanism of 65nm commercial MOS devices, using the node flip and recovery effect generated by multi-node charge sharing collection, the anti-SEU reinforcement design is realized at the physical layout level of the DICE flip-flop unit, achieving low cost, The purpose of low resource consumption and high reliability.

[0027] The specific flow of the DICE flip-flop design method is as follows:

[0028] (1) Adjust the physical position of the MOS tube of the cross-coupled inverter to reduce the recovery threshold of the latch of the flip-flop;

[0029] Among them, the specific method of adjusting the MOS transistor of the cro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com