Two-dimensional heterojunction array device and preparation method thereof

A two-dimensional heterojunction and heterojunction technology, which is applied in the fields of semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc. control, non-standard field effect transistors, etc., to achieve the effect of improving preparation efficiency and preparation yield, improving application value, and avoiding negative effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0064] The device-controllable preparation method of the metal-semiconductor heterojunction array is further given below, including the following steps:

[0065] Step 1, the Si / SiO 2 Substrates 1 and 2 were ultrasonically cleaned with organic solvents, followed by ultrasonic cleaning in the order of acetone (5-10min) → isopropanol (10-15min) → deionized water (10-20min), and finally cleaned the residue on the substrate with a nitrogen gun Dry with deionized water to get clean Si / SiO 2 base.

[0066] Step 2, Si / SiO obtained in the previous step 2 WSe grown on substrate 2 / SnS 2 vertical heterojunction. Si / SiO 2 The substrate is placed in a tube furnace, and the underlying material WSe is grown for the first time 2 , place the tungsten diselenide powder in the center of the furnace, and place a piece of SiO2 downstream of the quartz tube 2 / Si substrate. At the beginning, inject 400SCCM Ar gas into the tube for 15 minutes to ensure the stability of the chemical reaction...

Embodiment 1

[0072] An optical photo of an array device based on a metal-semiconductor heterojunction Figure 5 , as shown in 6 and 7, Figure 5 It is the corresponding physical figure in step 3 of the specific implementation mode, Figure 6 It is the corresponding physical figure in step 4 of the specific implementation mode, Figure 7 It is the physical diagram corresponding to the fifth step of the specific implementation manner.

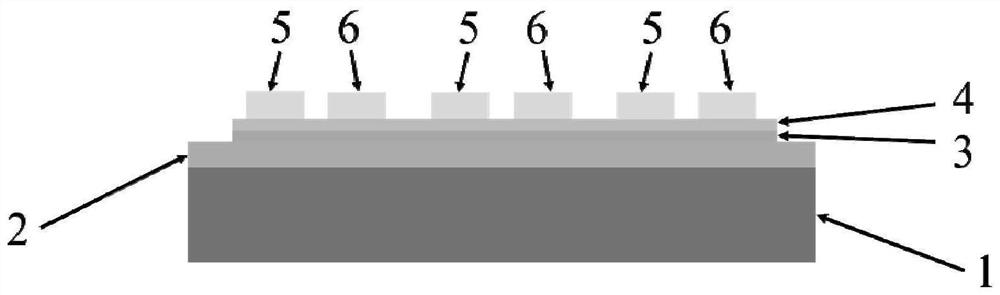

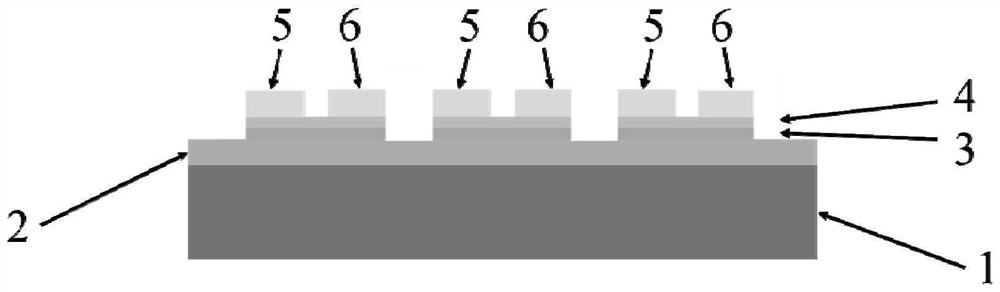

[0073] Such as Figure 5 As shown, from bottom to top including Si substrate 1, SiO 2 Insulation layer 2, channel material WSe 2 3. Contact material SnS 2 4. Positive and negative metal electrodes 5 and 6. The channel material WSe 2 3 and contact material SnS 2 4 in Si / SiO 2 On the substrate, obtained by a two-step vapor phase growth method, WSe 2 Material thickness is 1.5nm (two layers), SnS 2 The thickness of the material is 0.8nm (one layer). The electrode pattern is made by electron beam exposure, and the positive and negative electrodes 5 a...

Embodiment 2

[0078]Other conditions are all identical with embodiment 1. Only the plasma etching time is different (10s etching time).

[0079] Similarly, the obtained non-standard metal-semiconductor heterojunction array device is directly etched in the Plasma etching system, and the SnS on the upper layer of the channel is etched 2 etch away, leaving the channel material WSe 2 , while the contact material SnS under the metal electrode 2 are naturally preserved to improve the properties of individual devices. This completes the fabrication of an example metal-semiconductor heterojunction-based array device. The parameter of described Plasma etching is: Low power (knob selection gear Power 10%); Etching time is 10s; Etching gas selects N 2 and O 2 The mixed gas, the gas flow rate is 0.5NL / min.

[0080] Such as Figure 9 As shown, comparing the processing time of Plasma 10s and Plasma 20s, the maximum current value changed from 9.7μA to 10.2μA, basically remained unchanged, but the s...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com