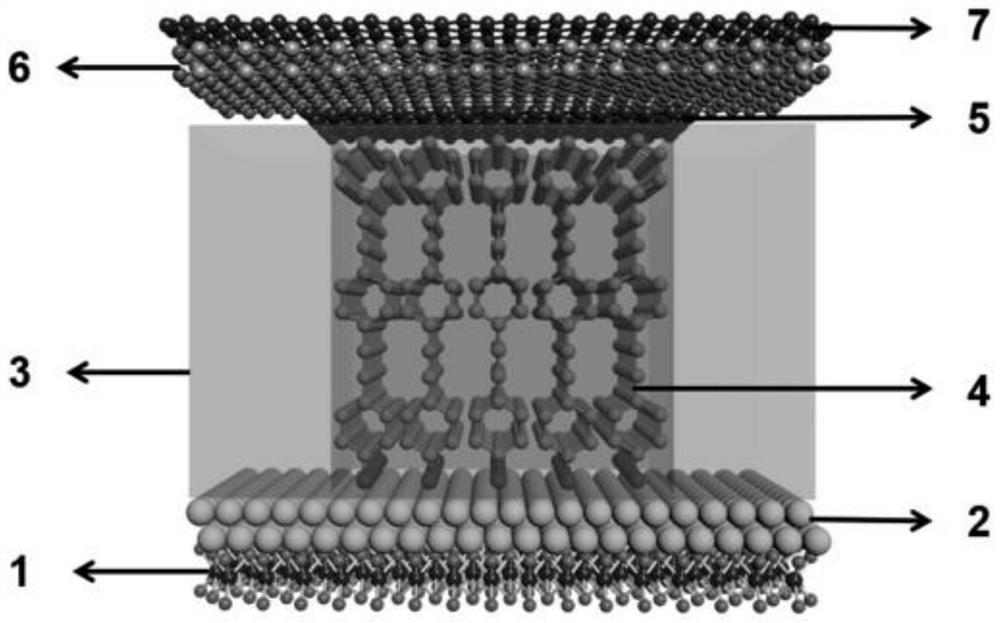

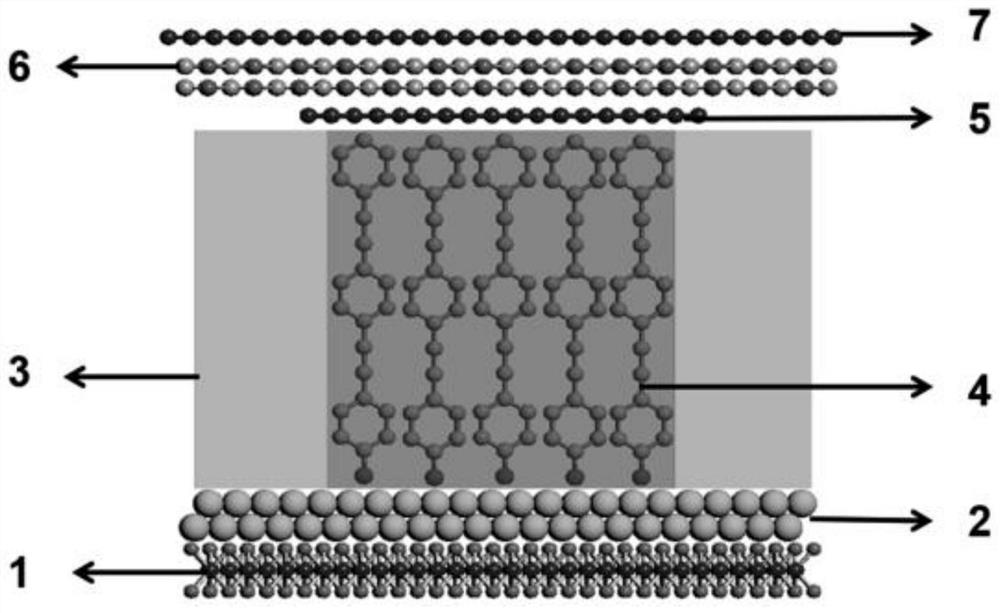

Vertical monomolecular film field effect transistor based on two-dimensional laminated heterostructure and preparation method of vertical monomolecular film field effect transistor

A field-effect transistor and heterostructure technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems of low gate regulation efficiency and poor stability, and achieve improved stability and flat atomic layer thickness , the effect of increasing the possibility of large-scale integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

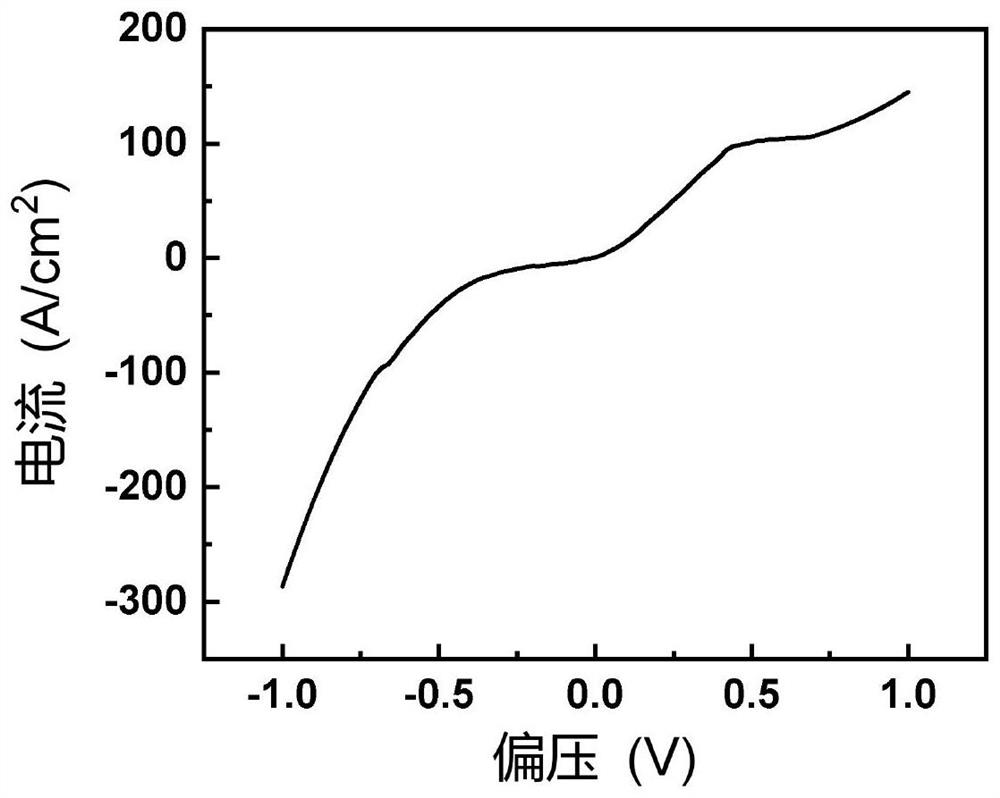

[0050] Example 1: Graphene drain / gate electrodes based on ultra-flat Au source electrodes and CVD growth, MoS 2 Vertical monomolecular film field effect transistor with template layer and h-BN insulating support layer / dielectric layer

[0051] 1. First, grow a large-area monolayer MoS on a silicon wafer by chemical vapor deposition (CVD) 2 film;

[0052] Then use an electron beam coater to coat the MoS 2 Evaporate 5-10nm gold film on the thin layer to obtain ultra-flat gold electrodes;

[0053] Then use CVD to grow single-layer h-BN (Nature, 2020, 579, 219) on the Cu(111) foil obtained by the annealing process, and repeat this step to obtain multiple single-layer (h-BN)-copper foils;

[0054] 2. Next, spin-coat PMMA glue on h-BN to form a PMMA-(h-BN)-copper foil sandwich structure;

[0055] 3. Then, put the structure into a 3% ammonium persulfate solution for etching. After the copper foil is dissolved, transfer the sample to clean deionized water to remove the residual am...

Embodiment 2

[0069] Example 2: Based on ultra-flat Au source electrode and mechanically exfoliated graphene drain / gate electrode, MoS 2 Vertical monomolecular film field effect transistor with template layer and h-BN insulating support layer / dielectric layer

[0070] 1. First, obtain one or few layers of MoS by mechanical exfoliation 2 , that is, repeated tearing with adhesive tape;

[0071] 2. Then, using polydimethylsiloxane (PDMS) as a transfer medium, the MoS 2 transferred to silicon substrates to obtain MoS 2 Template layer, used as a growth template for ultraflat gold films; specifically, MoS on tape contacted with polydimethylsiloxane (PDMS) on top of a glass slide 2 , when separated, MoS 2 A thin layer will remain on the PDMS. Tuning of MoS via a 3D translation stage in a microscope system 2 aligned with the silicon substrate. At this time, a slight force is applied to the glass slide, so that the MoS 2 Adhering to a silicon substrate, followed by slow detachment of PDMS, t...

Embodiment 3

[0084] Example 3: Graphene drain / gate electrodes based on ultra-flat Au source electrodes and CVD growth, WTe 2 Vertical monomolecular film field effect transistor with template layer and h-BN insulating support layer / dielectric layer

[0085] According to the steps of Example 1, only the MoS in the two-dimensional material template layer 2 Replaced by CVD grown WTe 2 The material obtains the graphene drain electrode / gate electrode based on ultra-flat Au source electrode and CVD growth provided by the present invention, WTe 2 Vertical monomolecular film field effect transistor with template layer and h-BN insulating support layer / dielectric layer.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com