Low-gate-resistance power MOSFET device with separated gate enhancement structure and method

A technology to enhance the structure and separate the gate, which is applied in the manufacturing of electrical components, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problems of large gate resistance and increase device switching loss, achieve low switching loss, reduce gate resistance value, The effect of increasing the effective cross-sectional area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

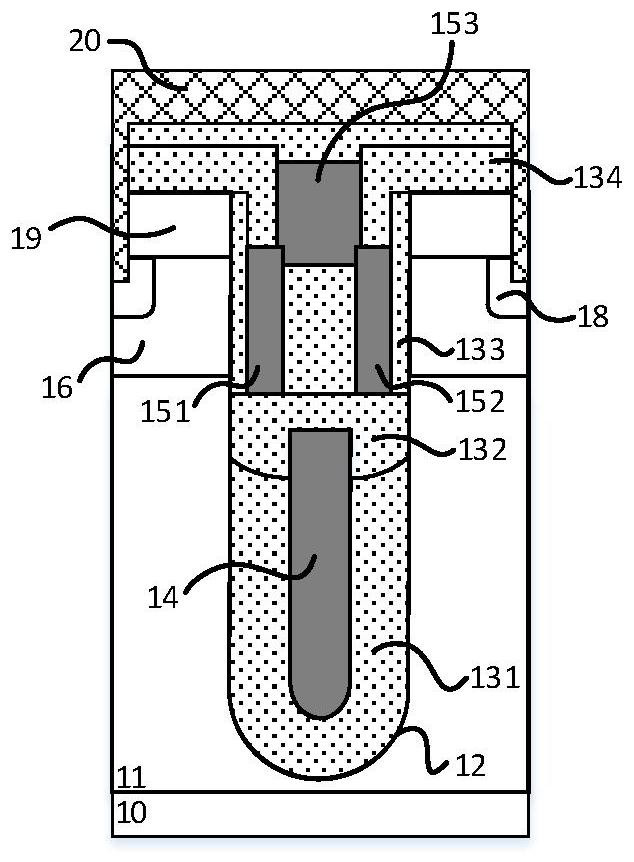

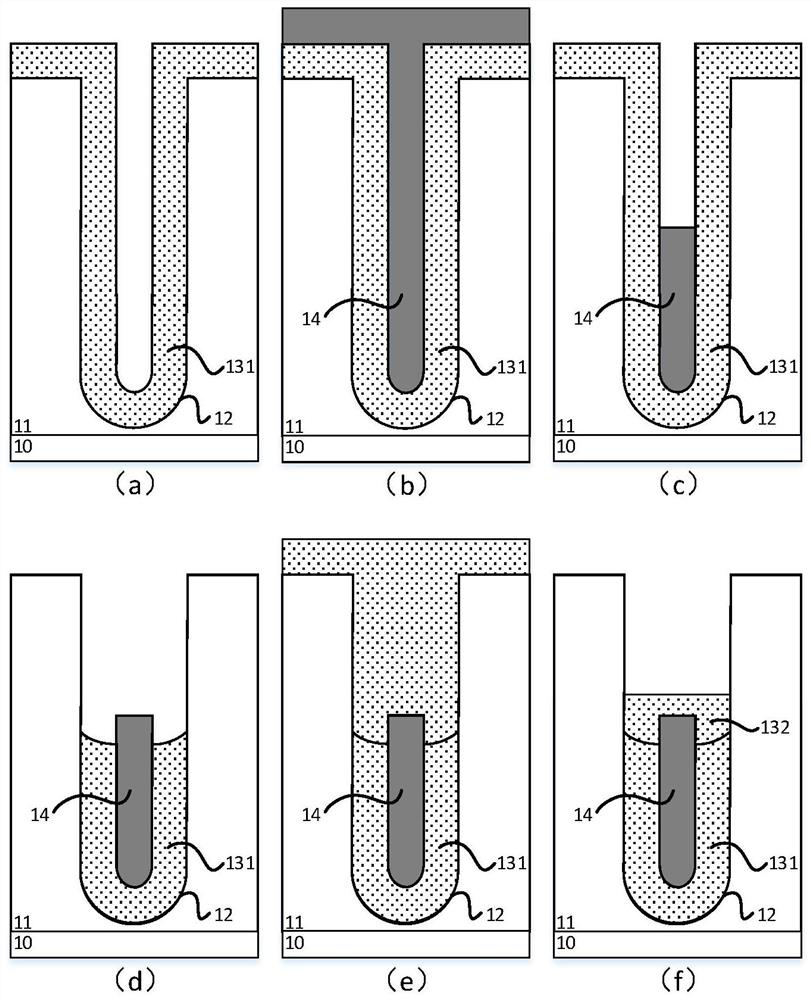

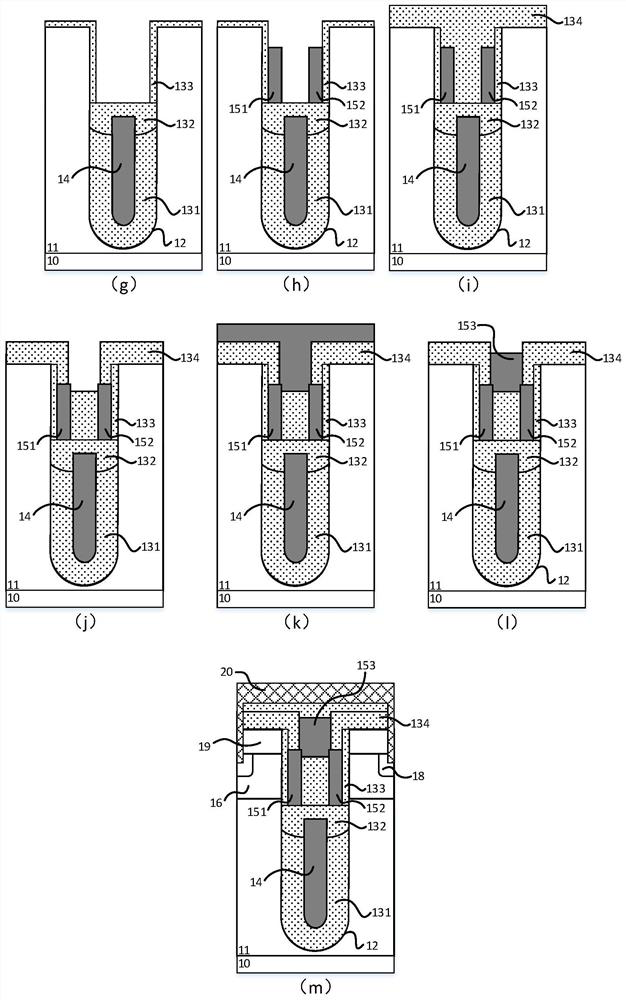

[0040] Such as figure 1As shown, a low gate resistance power MOSFET device with a split gate enhancement structure includes a first conductivity type substrate 10, a first conductivity type epitaxial layer 11 is formed on the upper surface of the first conductivity type substrate 10, and the first conductivity type epitaxial layer 11 is formed. There is a groove structure 12 in the layer 11, the groove structure 12 includes a control gate electrode and a separation gate electrode 14, the control gate electrode includes a first gate electrode 151, a second gate electrode 152 and a third gate electrode 153, the first gate electrode 151 and the separation gate electrode 14. The second gate electrode 152 is located above the separated gate electrode 14, and is separated from the separated gate electrode 14 by the second dielectric layer 132. The second conductivity type well region 16 is separated, the third gate electrode 153 is located above the first gate electrode 151 and the ...

Embodiment 2

[0055] Such as image 3 As shown, the difference between this embodiment and the structure described in Embodiment 1 is that the second dielectric layer 132 is a low-k dielectric, which can further reduce the gate-source capacitance.

Embodiment 3

[0057] Such as Figure 4 As shown, the difference between this embodiment and the structure described in Embodiment 1 is that the second dielectric layer 132 is a low-k dielectric, and the first dielectric layer 131 is a low-k dielectric, and the entire separation gate electrode is surrounded by a low-k dielectric, which can Further reduce gate-source capacitance and source-drain capacitance.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com