Method for reducing wire length, electronic equipment and computer readable storage medium

A computer program and line length technology, which is applied in the field of EDA tools for integrated circuit layout design, can solve problems such as large influence of physical wiring, and achieve the effect of reducing line length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

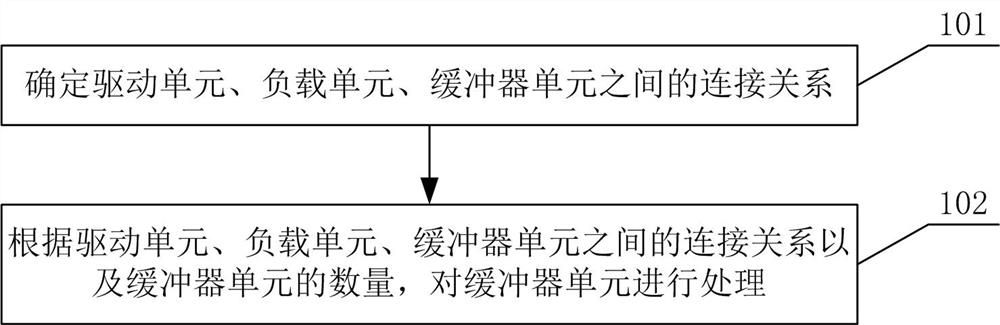

[0029] figure 1 For the method flowchart according to the reduction line length of the present invention, below will refer to figure 1 , the method for reducing the wire length of the present invention is described in detail.

[0030] First, in step 101, the connection relationship among the driving unit, the load unit and the buffer unit is determined.

[0031] In the embodiment of the present invention, after the rationalized layout engine determines the placement position of the buffer unit (Buffer), it is necessary to determine whether the position of the Buffer unit is within the span range of the drive unit (Source unit) and the load unit (Sink) in the x direction. unit) range.

[0032] In step 102, the buffer units are processed according to the connection relationship among the drive unit, the load unit, and the buffer units and the number of the buffer units.

[0033] In the embodiment of the present invention, if the position of the Buffer unit is within the range...

Embodiment 2

[0043] In the embodiment of the present invention, it is assumed that a certain line network in the circuit: Source is a driving unit, and Sink is a load unit. In order to optimize the timing target from Source to Sink, three buffer units are inserted in the middle, and the target positions of the three buffer units on the chip unit row have been obtained.

[0044] The first step is to determine the connection relationship between the drive unit, load unit and buffer unit as follows:

[0045] Source->Buffer3->Buffer2->Buffer1->Sink.

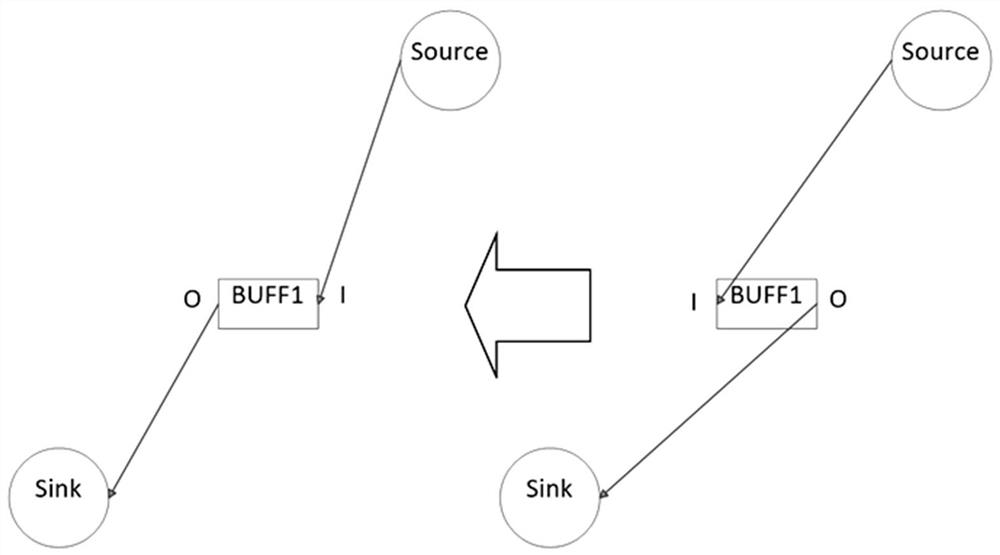

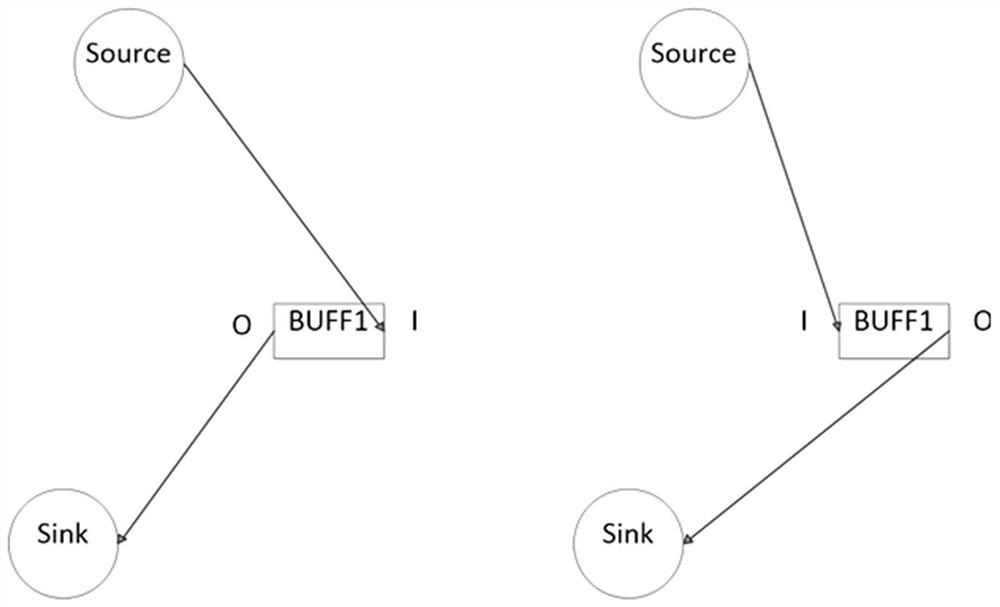

[0046] In the second step, the buffer unit Buffer1 is processed. Check if the output O pin of Buffer1 is closer to the sink unit than the input I pin. If not, perform a horizontal unit flip on the buffer unit Buffer1 so that the O pin is closer to the Sink unit.

[0047] The third step is to process the buffer unit Buffer2. Check that the output O pin of Buffer2 is closer to the Buffer1 cell than the input I pin. If not, perform a horizontal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com