Method for covalently grafting fluorine-free nano-pore low k dielectric film on surface of semiconductor

A surface covalent, dielectric thin film technology, applied in nanotechnology for materials and surface science, semiconductor/solid-state device manufacturing, nanotechnology, etc., can solve problems such as the inability to achieve low dielectric constant, and prevent strong corrosion. Function, composition controllable, thickness controllable effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0046] This embodiment relates to a method for covalently grafting a low k dielectric film on the surface of a semiconductor based on diazonium salt technology. The semiconductor substrate can be silicon, germanium, or gallium arsenide (specifically, silicon is selected as the substrate in this embodiment), specifically The implementation steps are as follows:

[0047] Step (1): Under the condition of a temperature of 20° C., the semiconductor substrate is ultrasonically cleaned sequentially with acetone, alcohol and deionized water, and the cleaning time is 5 minutes each time;

[0048] Step (2): Place the cleaned semiconductor substrate in a 3v% HF solution at a temperature of 20°C for 1 min;

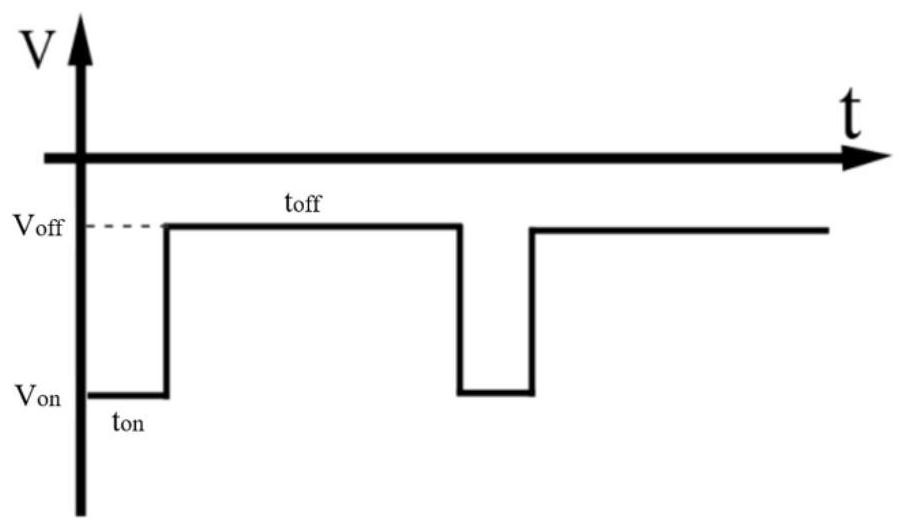

[0049] Step (3): At a temperature of 20°C, immerse the corroded semiconductor surface directly into the prepared chemical solution ① for surface passivation. The immersion time is 30s, so that the semiconductor surface is transformed into a passivation layer surface, thereby preventin...

Embodiment 2

[0058] This embodiment relates to a method for covalently grafting a low k dielectric film on a semiconductor surface based on diazonium salt technology. The semiconductor substrate is silicon, and the specific implementation steps are as follows:

[0059] Step (1): Under the condition of a temperature of 20° C., the semiconductor substrate is ultrasonically cleaned sequentially with acetone, alcohol and deionized water, and the cleaning time is 5 minutes each time;

[0060] Step (2): Place the cleaned semiconductor substrate in a 0.5v% HF solution at a temperature of 20°C for 10 minutes;

[0061] Step (3): At a temperature of 20°C, directly immerse the corroded semiconductor surface in the prepared chemical solution ① for surface passivation. The immersion time is 30s, so that the semiconductor surface is transformed into a passivation layer surface, thereby preventing The surface is oxidized in the next reaction;

[0062] The configuration process of the chemical solution ①...

Embodiment 3

[0067] This embodiment relates to a method for covalently grafting a low k dielectric film on a semiconductor surface based on diazonium salt technology. The semiconductor substrate is silicon, and the specific implementation steps are as follows:

[0068] Step (1): Under the condition of a temperature of 20° C., the semiconductor substrate is ultrasonically cleaned sequentially with acetone, alcohol and deionized water, and the cleaning time is 5 minutes each time;

[0069] Step (2): at a temperature of 20°C, place the cleaned semiconductor substrate in a 5% volume fraction of HF solution, and soak for 1 min;

[0070] Step (3): At a temperature of 20°C, immerse the corroded semiconductor surface directly in the prepared chemical solution ① for surface passivation. The passivated semiconductor surface is oxidized in the next reaction;

[0071] The configuration process of the chemical solution ① is as follows: add 100ml deionized water to the Teflon beaker, then add 0.2g sodi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com