SiC MOSFET packaging structure optimization design method, medium and equipment

A packaging structure and optimization design technology, applied in design optimization/simulation, computer-aided design, calculation, etc., can solve problems such as accelerated wire peeling, solder cracks, etc., to achieve high design efficiency, improve device structure, and improve the effect of analysis efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

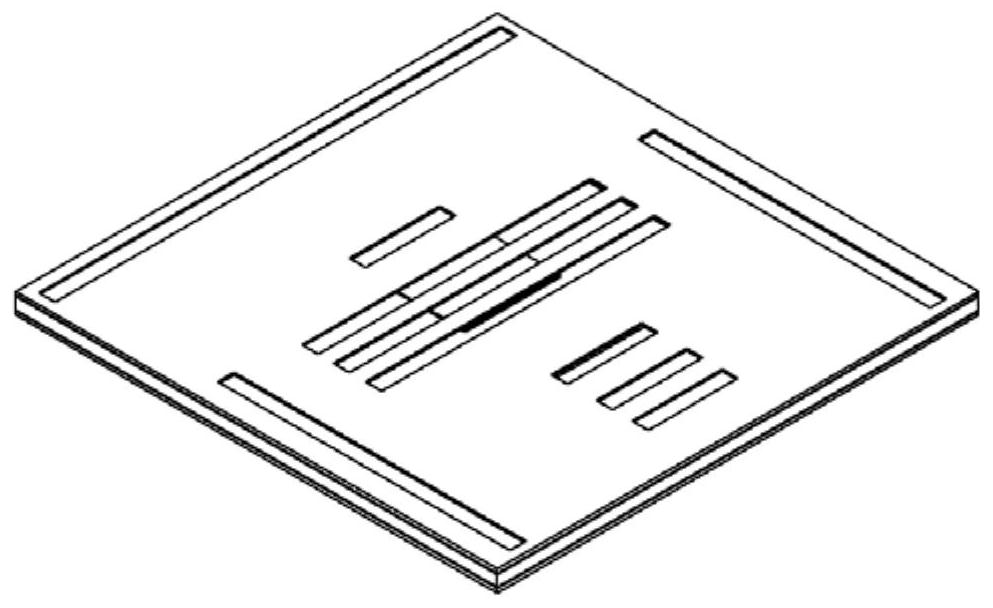

[0035] This embodiment provides a method for optimizing the packaging structure of an embedded fan-out SiC MOSFET, which is mainly applied to occasions for optimizing the reliability of power devices and modules. This method uses the response surface method to optimize the design and analysis of the simulation. Based on the finite element simulation analysis, the maximum heat dissipation temperature of the redistribution layer (RDL) in the SiC MOSFET in the steady state heat dissipation and the maximum stress after the temperature cycle simulation are calculated. The mathematical model between the distribution of the chip and the heat dissipation temperature and the maximum stress, so as to find out the optimal chip distribution mode for heat dissipation and stress, so as to achieve the purpose of optimization.

[0036] Such as figure 1 As shown, the method includes the following steps:

[0037] Step 1: Establish a three-dimensional model of the SiC MOSFET device, and determi...

Embodiment 2

[0057] This embodiment provides a computer-readable storage medium, on which a computer program is stored, and when the computer program is executed by a processor, the steps of the method for optimizing the packaging structure of an embedded fan-out SiC MOSFET as described in Embodiment 1 are realized. .

Embodiment 3

[0059] The present invention also provides an electronic device, comprising a processor and a memory storing processor-executable instructions, wherein the processor is coupled to the memory for reading program instructions stored in the memory, and in response, The steps in the method for optimizing the packaging structure of the embedded fan-out SiC MOSFET described in Embodiment 1 are performed.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com