On-chip monitoring circuit of anti-fuse FPGA

A monitoring circuit and anti-fuse technology, applied in hardware monitoring, electrical digital data processing, error detection/correction, etc., can solve problems such as difficulty in accurately monitoring signal transmission speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

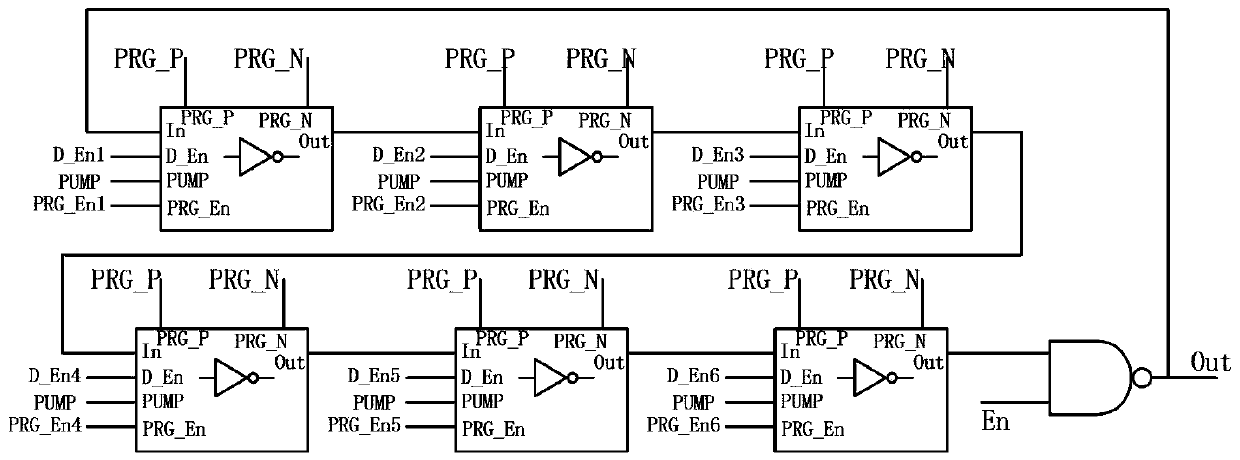

[0032] The invention provides an on-chip monitoring circuit of an antifuse FPGA, its structure is as follows: figure 1 As shown, it includes an even-numbered delay unit circuit and a NAND gate circuit; in the first embodiment, the number of the delay unit circuits is 6, and the output terminal of a delay unit circuit is connected to the next delay unit circuit. The input end of the time unit circuit, 6 described delay unit circuits are connected in series to an input end of the NAND gate circuit; the other input end of the NAND gate circuit is connected to the monitoring enable signal En; The output end of the NAND gate circuit is connected to the input end of the first delay unit circuit to form a ring circuit. When the monitoring enable signal En was low, the on-chip monitoring circuit of the antifuse FPGA output a fixed high level and stopped working; when the monitoring enabling signal En was high, the on-chip monitoring circuit of the antifuse FPGA start working. Specif...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com