Tensor processor instruction set architecture

A processor and machine instruction technology, applied in the field of tensor processor instruction set architecture, can solve the problem of expensive machine learning

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

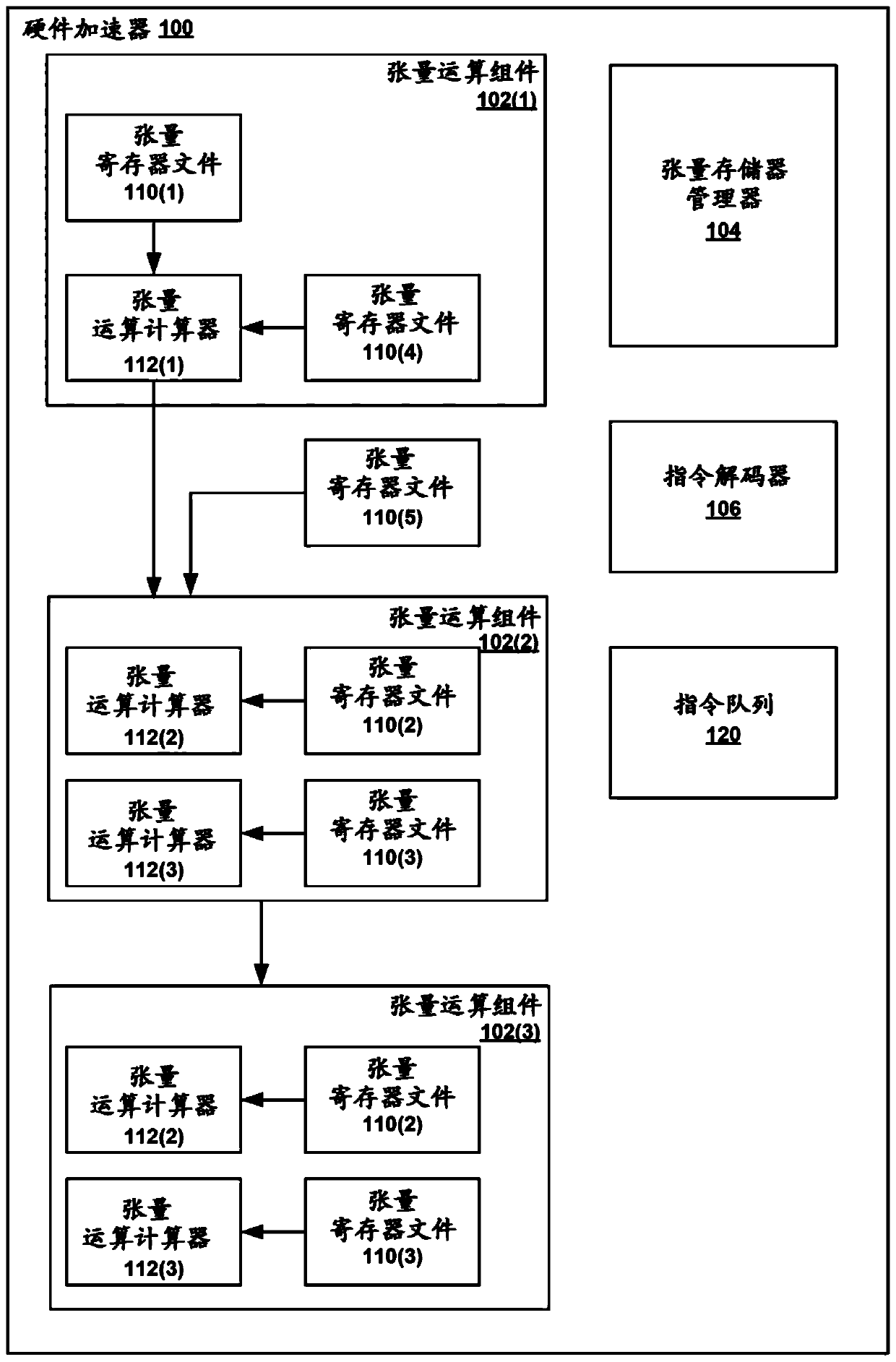

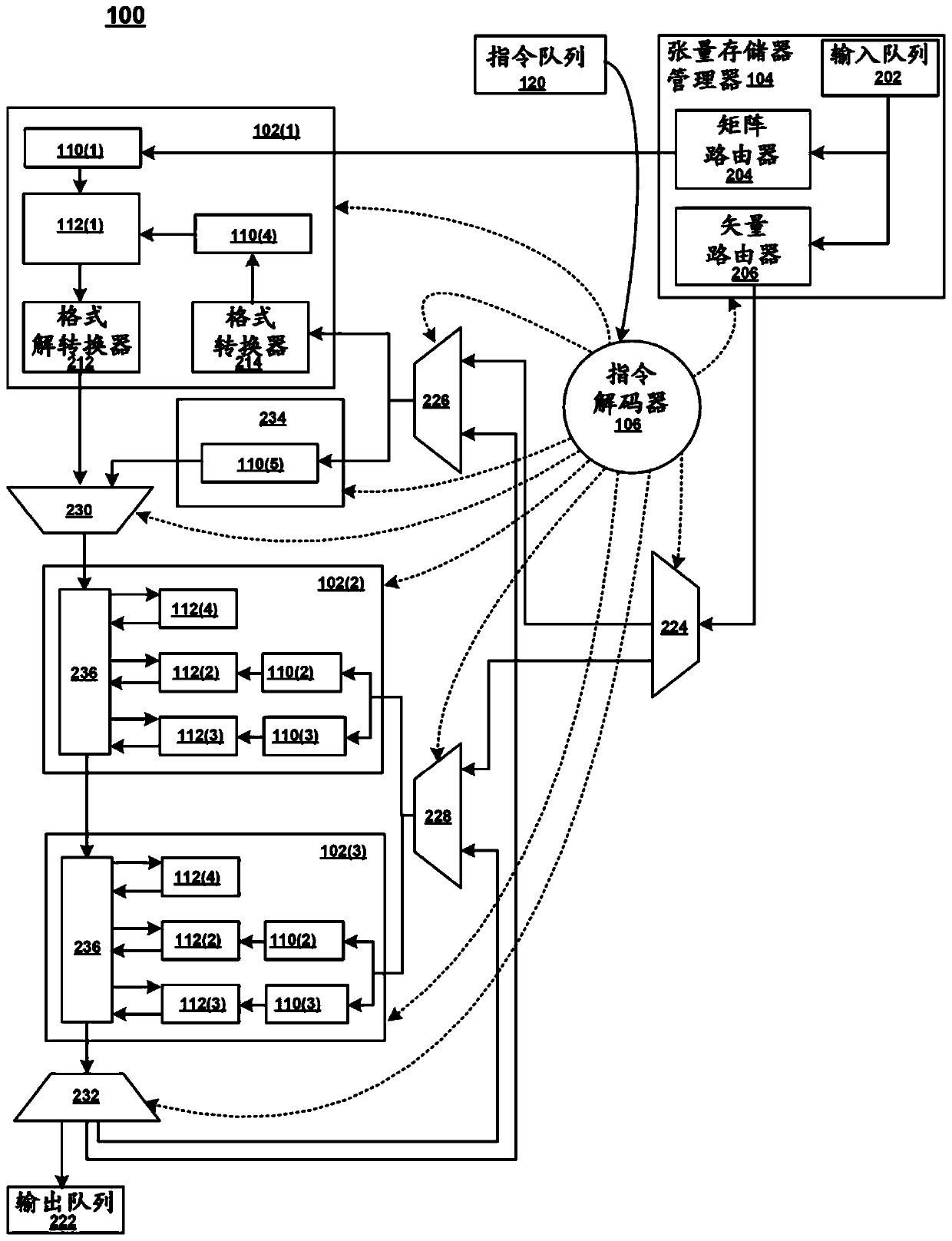

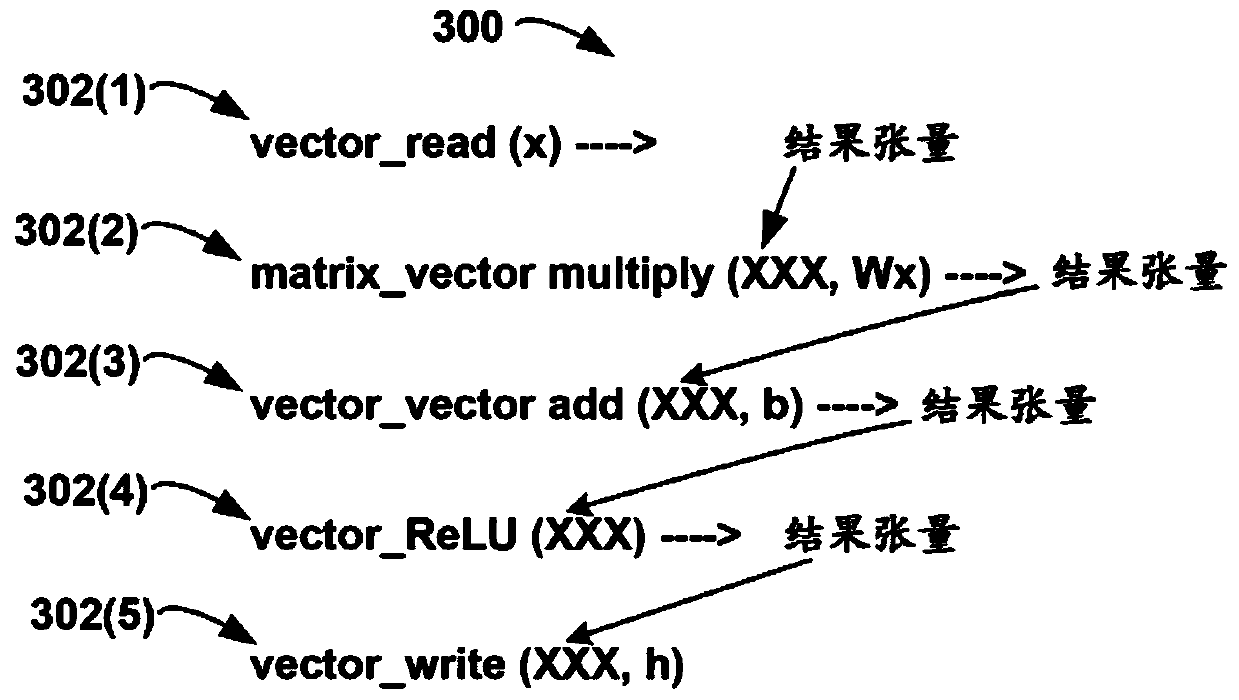

[0020] Certain embodiments of the present technology involve hardware accelerators. Some embodiments relate to tensor register files in hardware accelerators. Some embodiments of the present technology relate to instruction set architectures in hardware accelerators.

[0021] Hardware accelerators can have various tensor operation calculators to perform various types of tensor operations. Tensor operations calculators may require tensors in order to operate on them. Efficient computations can be significantly slowed down if the tensor calculator has to wait for the required tensors to be provided.

[0022] In some embodiments, instead of having one large tensor register file storing tensors for all types of tensor operations, a hardware accelerator has multiple smaller tensor register files. These smaller tensor register files can be dedicated to one instance of the tensor calculator. Such a configuration can improve bandwidth by keeping the various tensor calculators busy...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com