A Configurable Hybrid Heterogeneous Computing Core System for Multi-Domain Chip Design

A chip design and computing core technology, applied in computing, memory systems, multiprogramming devices, etc., can solve the problems of inability to run new algorithms, lack of flexibility in custom chips, and inability to achieve high performance and efficiency in overall applications. Efficiently create effects that reduce design time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention is described in further detail now in conjunction with accompanying drawing.

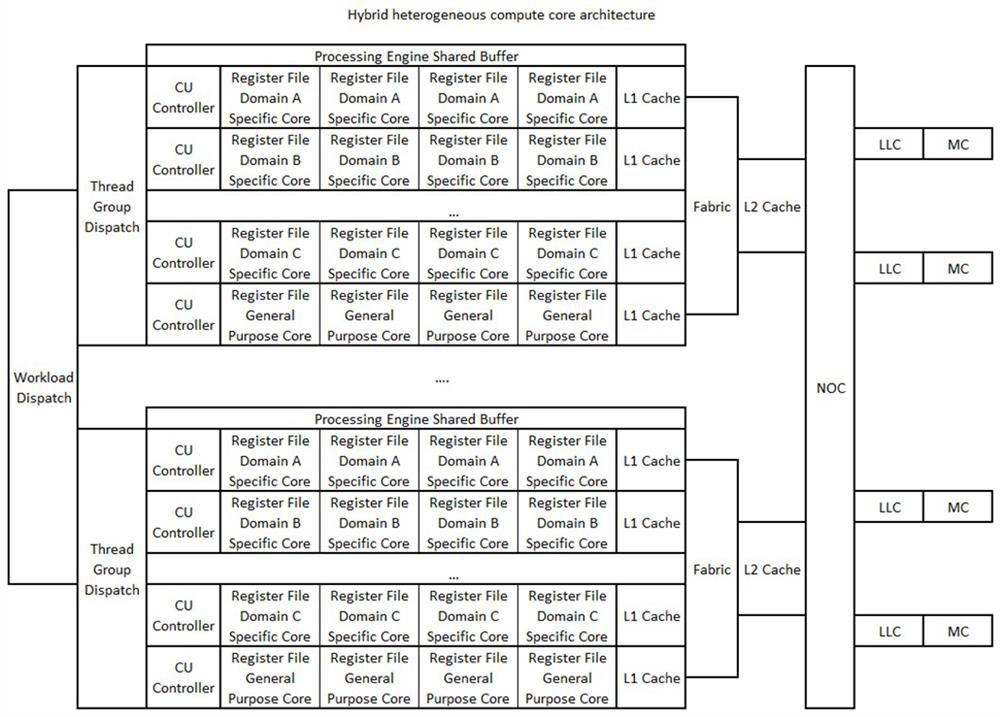

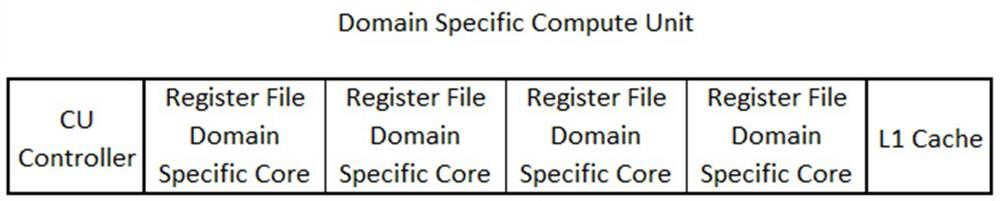

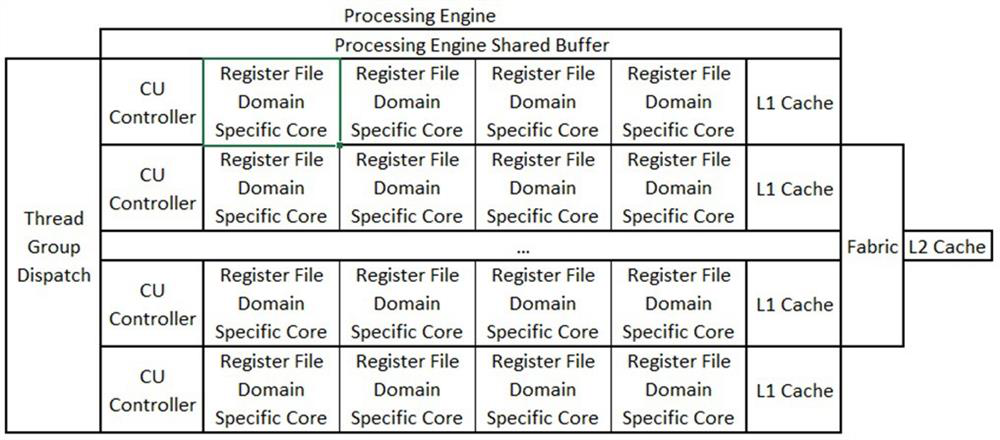

[0019] Such as figure 1 A configurable hybrid heterogeneous computing core system architecture for multi-domain chip design shown, creating efficient cores for each domain. Each domain-specific core has its own register file (Register File), and a group of domain-specific cores share the L1 cache (L1 Cache). The group of cores and their CU controller (CU Controller), register file, and L1 cache are called Domain Specific Compute Unit (DSCU). figure 2 is a schematic diagram of the DSCU. The processing engine (Processing Engine, PE) includes a thread group scheduling module, some DSCUs, an L2 cache (L2Cache), and a Fabric architecture that connects the L1 cache in the DSCU to the L2 cache. Figure 3a is the schematic diagram of PE. In PE, DSCU can be used in different fields. For example, in Figure 3b Among them, 3 DSCUs are used for artificial intelligence convolu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com