Interstage gain mismatch correction method for pipelined ADC

A mismatch correction and pipeline technology, applied in analog/digital conversion calibration/testing, analog-to-digital converters, electrical components, etc., can solve problems such as large limitations, achieve high real-time performance and improve accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In conjunction with the accompanying drawings, the present invention is further illustrated through the embodiments.

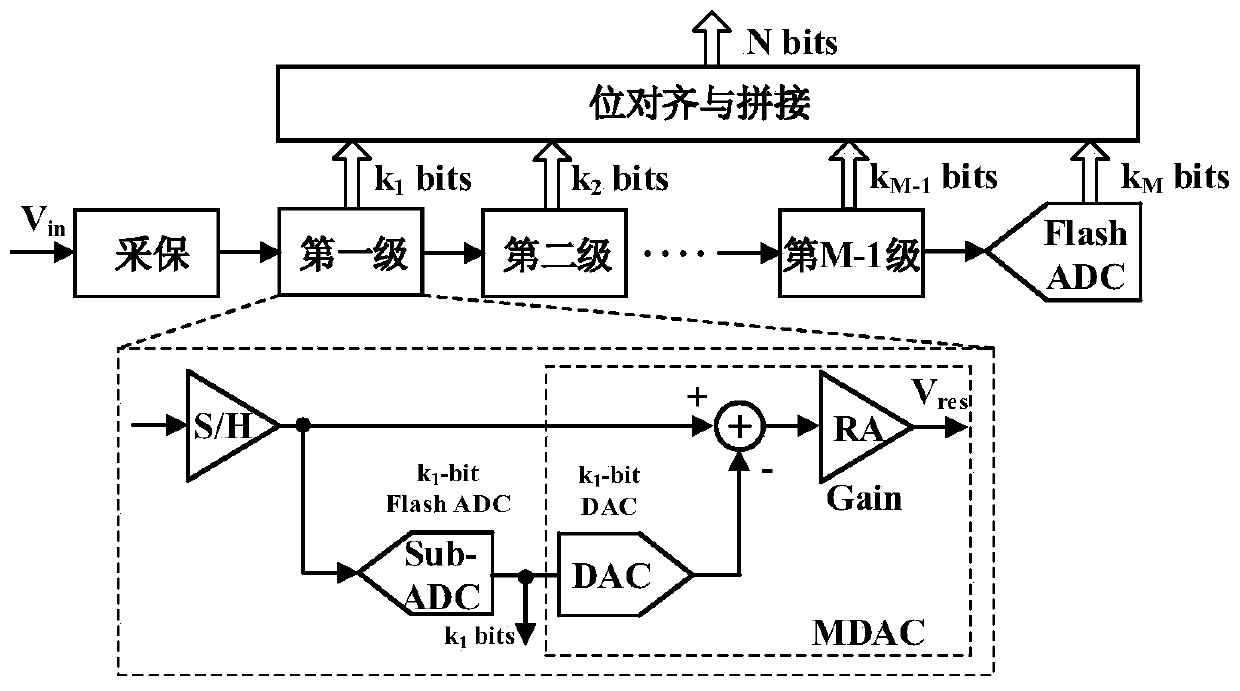

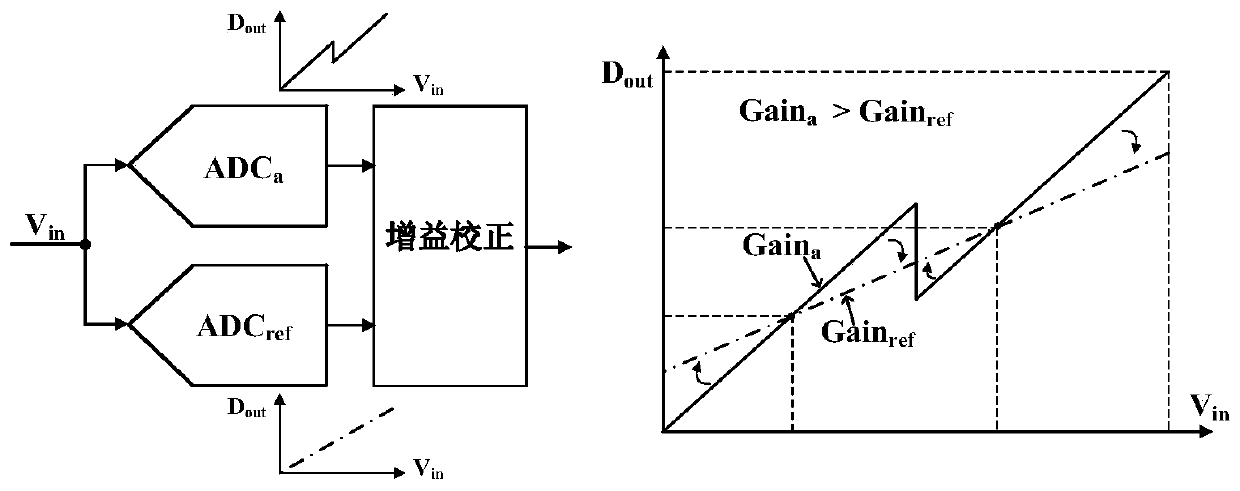

[0042] The gain mismatch in the pipeline ADC will cause non-ideal gaps or steps in the output of the pipeline ADC. Gain mismatch can be corrected by compensating for gaps or steps so that the overall output remains linear. Based on this, if figure 2 As shown, if there is a reference channel and the correction channel to quantize the same input signal at the same time, and the reference channel is ideal, that is, the output is linear, then the inter-stage gain coefficient m can be modified through the digital background 1 , so that the output of the calibration channel maintains the same slope as the reference channel, that is, the same linearity.

[0043] D. out =D 1 +m 1 ·D BE

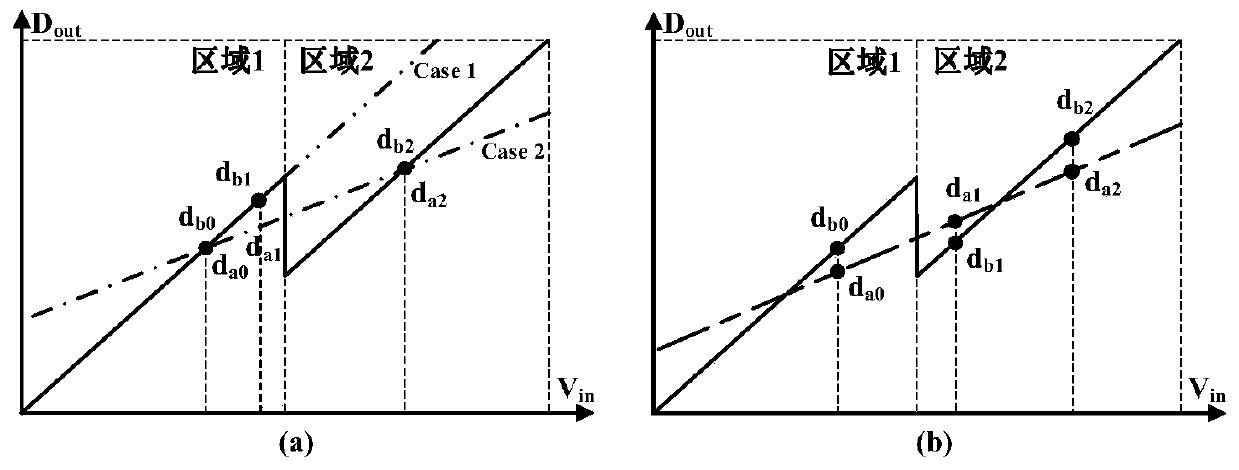

[0044] Taking the correction of the inter-stage gain mismatch between the i+1-th pipeline and the i-th pipeline of the correction channel in the pipeline ADC as an exam...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com