IGBT with self-biased separation gate structure

A separate gate and self-bias technology, which is applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problem of slow switching speed of devices, achieve the effects of reducing switching loss, increasing switching speed, and reducing gate capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

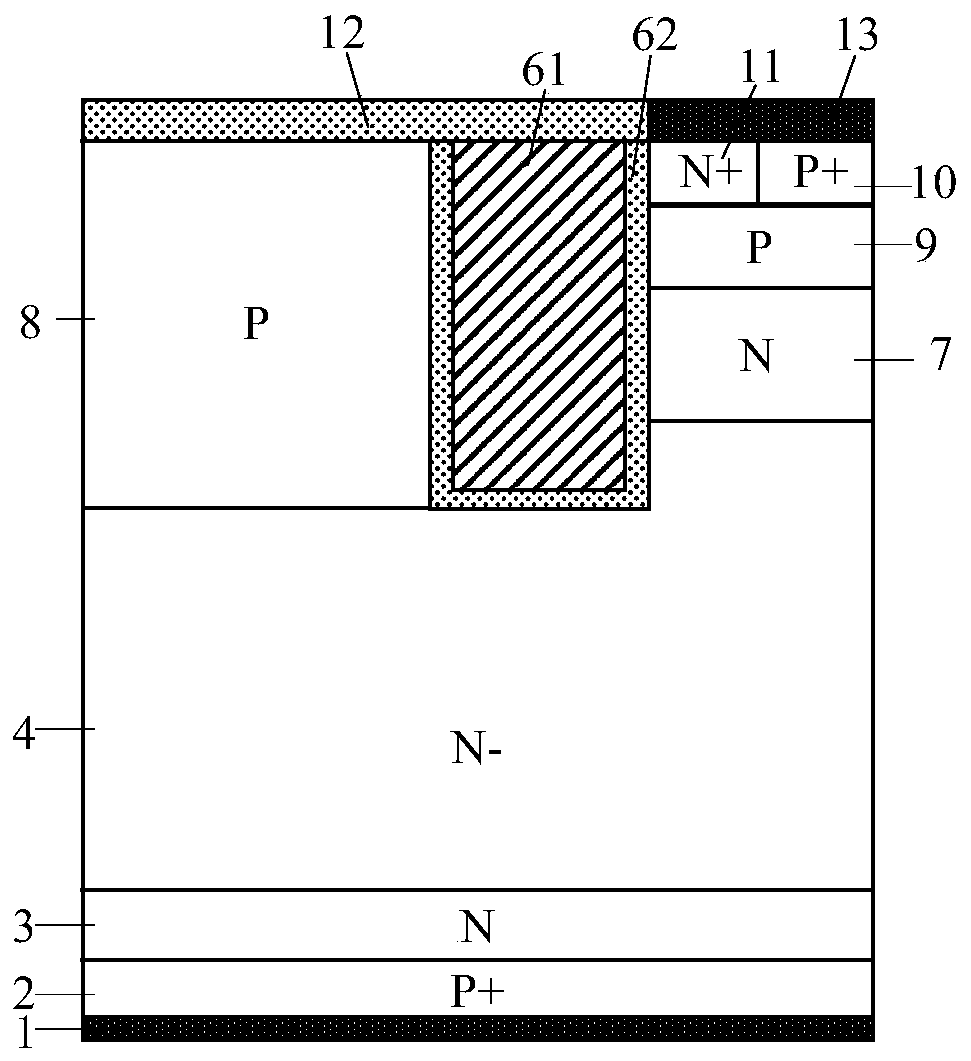

[0024] An IGBT with a self-biased split gate structure, its half-cell structure is as follows figure 2 As shown, it includes collector metal 1; N-type field stop layer 2 located on the upper surface of collector metal 1; N-drift region 4 located above N-type field stop layer 3; The P-type floating region 8; the metal 142 located on the upper surface of the P-type floating region 8; the N-type charge storage layer 7 located on the other side above the N-drift region, and the doping concentration of the N-type charge storage layer is greater than or Equal to the doping concentration of the N-drift region 4; the P-type base region 9 located on the upper surface of the N-type charge storage layer; the N+ emitter region 11 and the P+ emitter region 10 located side by side on the upper surface of the P-type base region 9 and independent of each other; The emitter metal 13 on the upper surface of the N+ emitter region 11 and the P+ emitter region 10; the trench structure on one side...

Embodiment 2

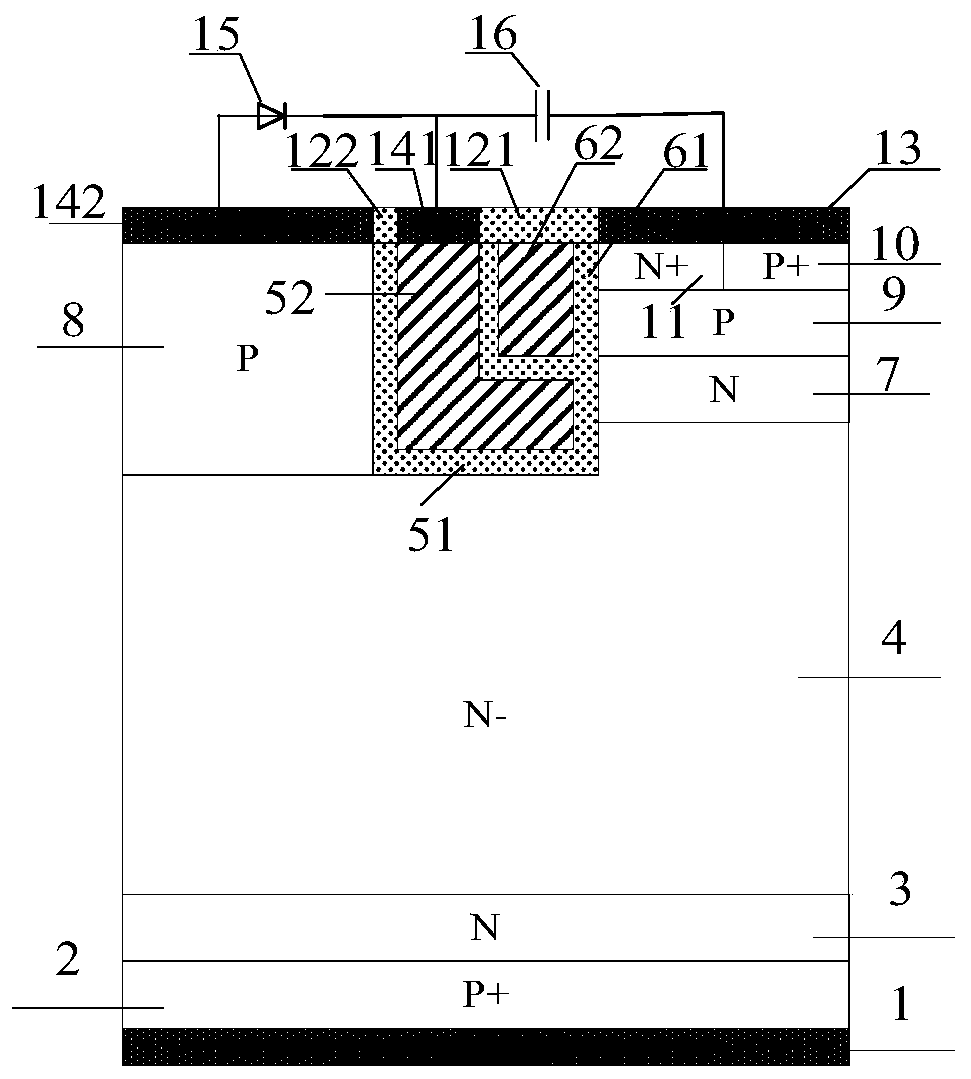

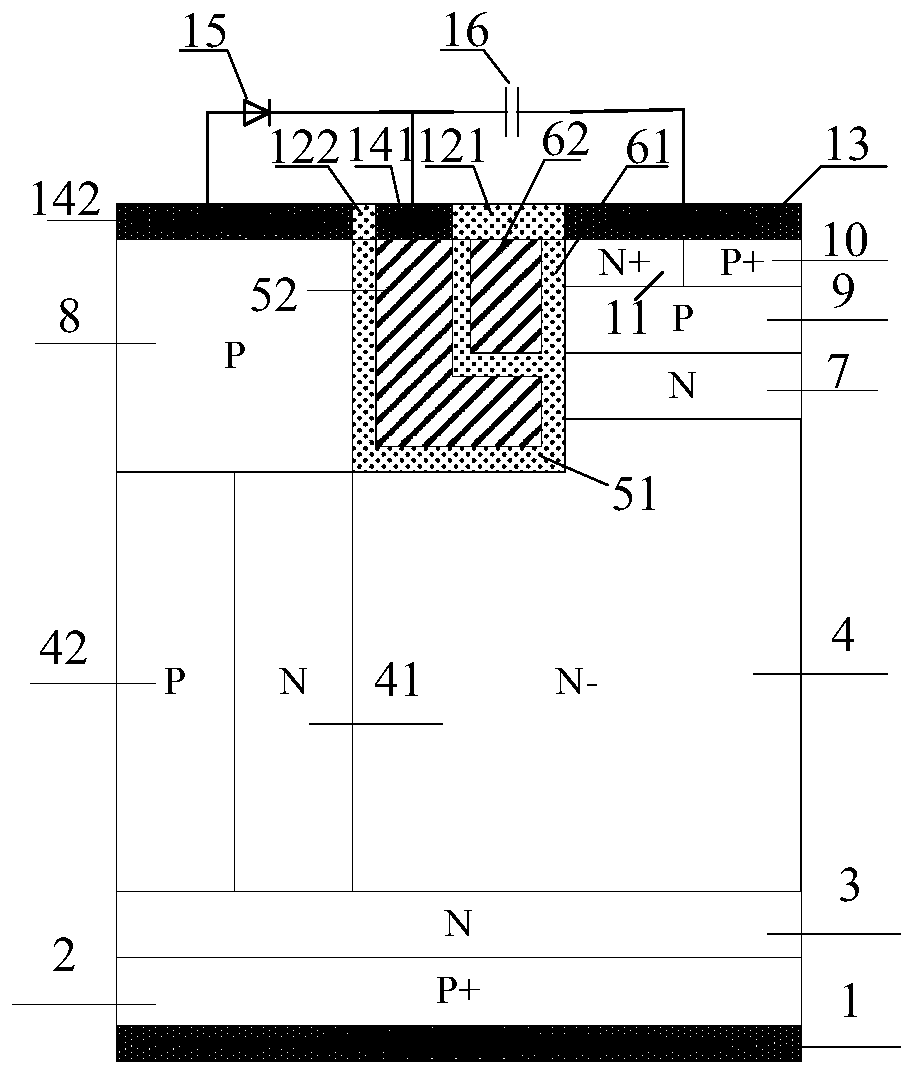

[0026] An IGBT with a self-biased split gate structure, its half-cell structure is as follows figure 2As shown, it includes collector metal 1; N-type field stop layer 2 located on the upper surface of collector metal 1; N-drift region 4 located above N-type field stop layer 3; The P-type floating region 8; the metal 142 located on the upper surface of the P-type floating region 8; the N-type charge storage layer 7 located on the other side above the N-drift region; the P-type base region located on the upper surface of the N-type charge storage layer 9; N+ emitter regions 11 and P+ emitter regions 10 placed side by side on the upper surface of the P-type base region 9 and independent of each other; emitter metal 13 located on the upper surfaces of the N+ emitter region 11 and P+ emitter region 10; located in the P-type floating region The trench structure on one side includes a separation gate dielectric layer 51, a separation gate electrode 52, the depth of the separation ga...

Embodiment 3

[0028] An IGBT with a self-biased split-gate structure with a half-cell structure such as Figure 4 As shown, on the basis of Embodiment 1, the diode 15 is integrated on the surface of the IGBT, and the P+ region 151 and the N+ region 152 that are placed side by side on the upper surface of the medium 122 and are independent from each other, and the metal 142 connected to the P+ region 151, and the N+ region 152 Connected metal 142 forms a diode.

[0029] Integrating the diode 15 into the IGBT reduces the packaging area of the chip and improves the integration of the chip.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com