Three-dimensional optoelectronic integrated optical grating coupler realized based on CMOS post-process and preparation method thereof

A grating coupler and optoelectronic integration technology, applied in the direction of optical waveguide light guide, light guide, optics, etc., can solve the problem of increasing optical coupling loss and achieve the effect of increasing bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to make the objectives, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

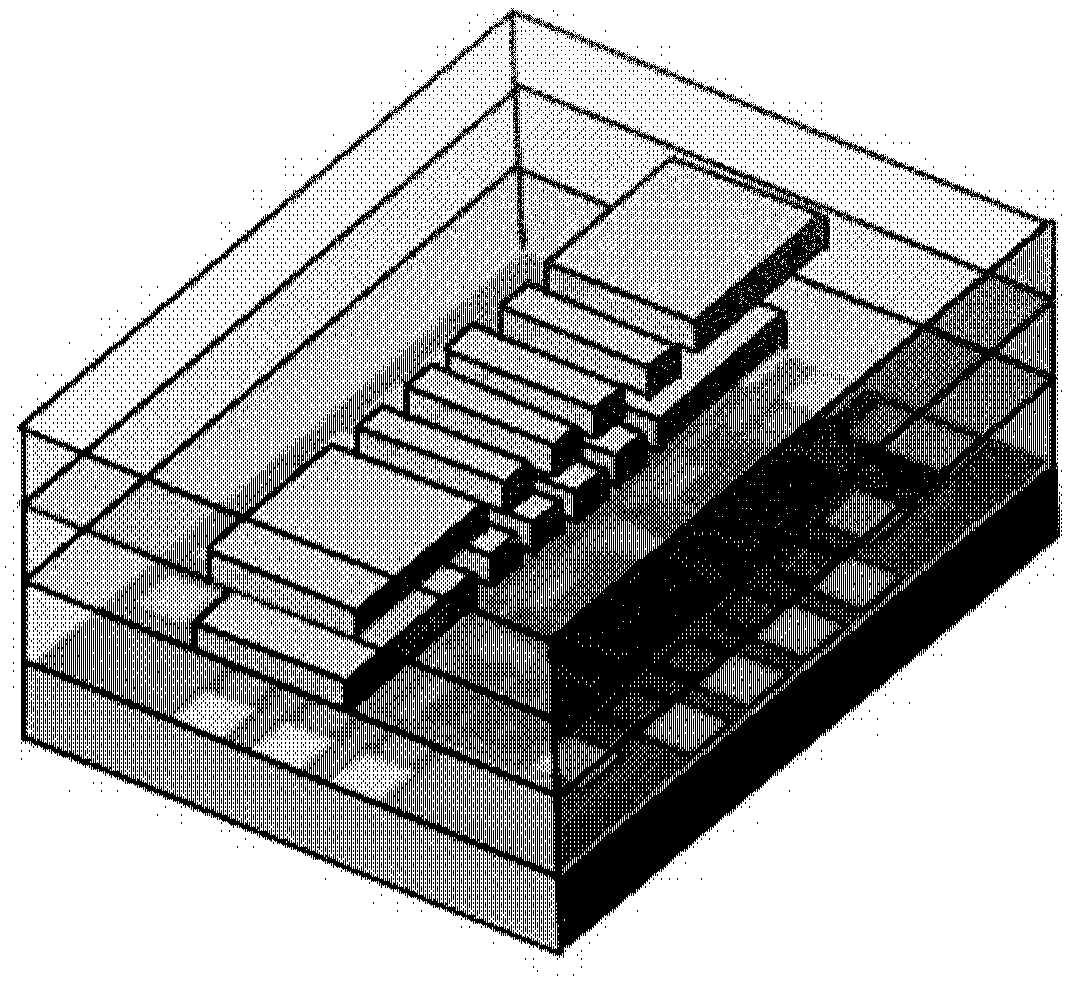

[0041] The present invention proposes a three-dimensional photoelectric integrated grating coupler realized based on CMOS post-process. All process temperatures are controlled below 400°C to avoid impact on CMOS integrated circuits, realize monolithic integration of photoelectric devices and CMOS integrated circuits, and realize three-dimensional Optical interconnection solves the bottleneck problem of electrical interconnection.

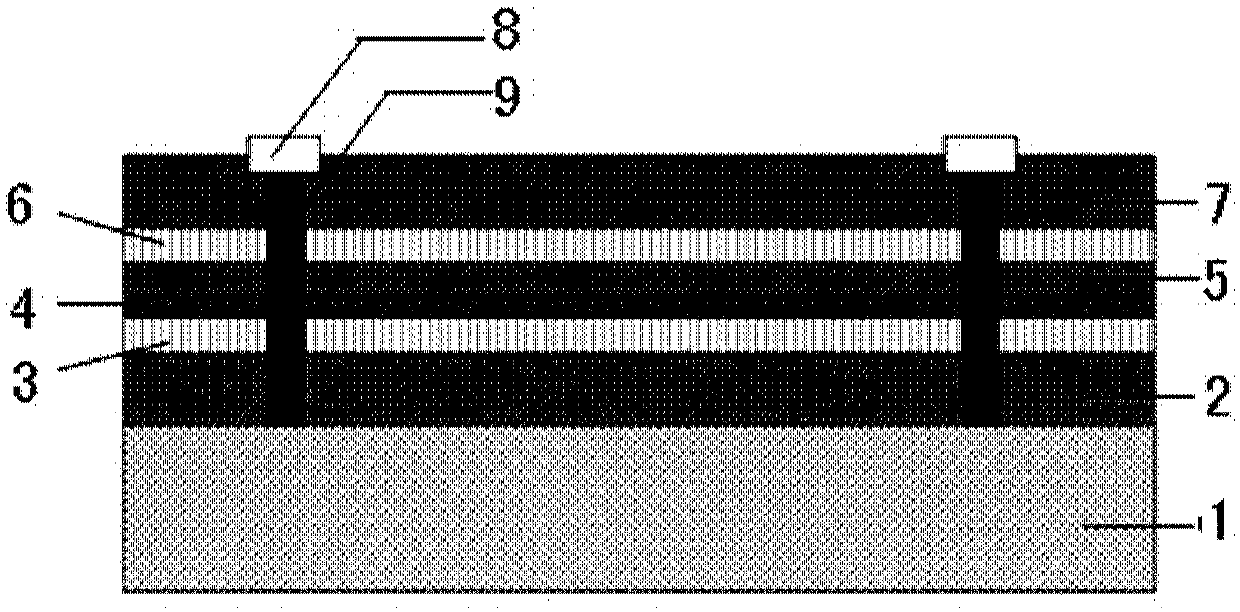

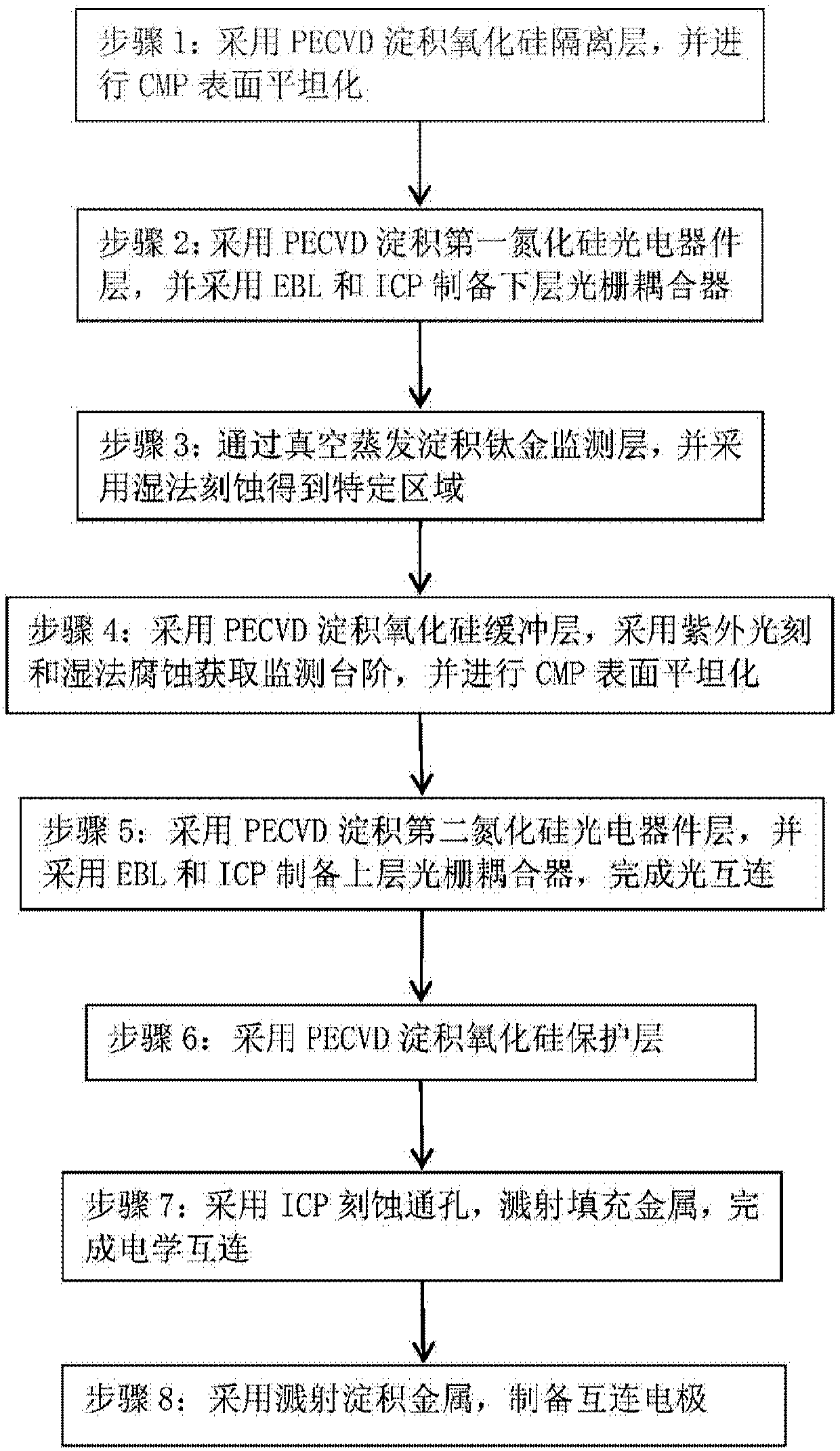

[0042] Reference figure 1 with figure 2 The three-dimensional photoelectric integrated grating coupler realized by the present invention based on the CMOS post process includes a silicon oxide isolation layer 2, a first silicon nitride photoelectric device layer 3, and a titanium-gold monitorin...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com