Semiconductor device and method for manufacturing same

A manufacturing method, semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as poor moisture resistance, difficulty in ensuring solderability, poor connection reliability, etc., to ensure Solderability, quality and reliability improvement effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

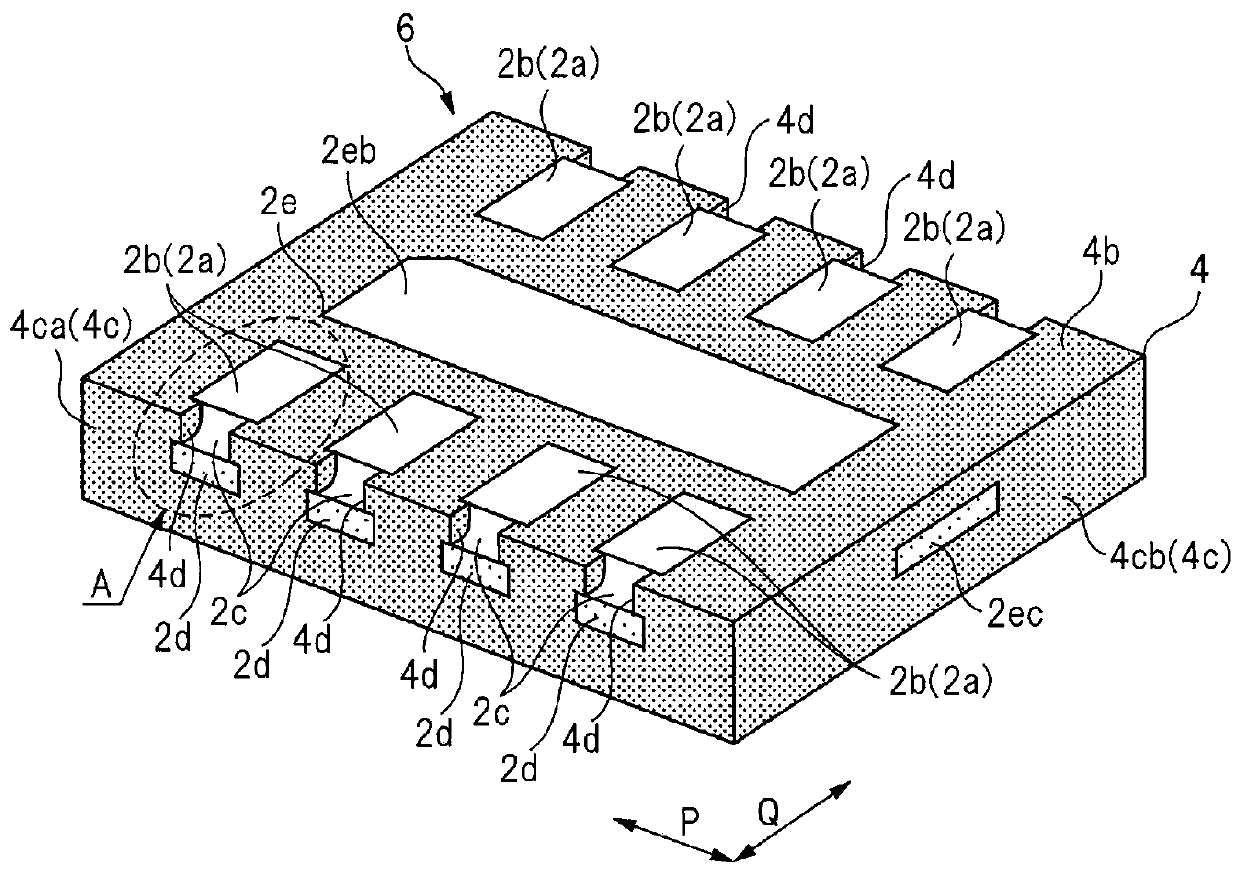

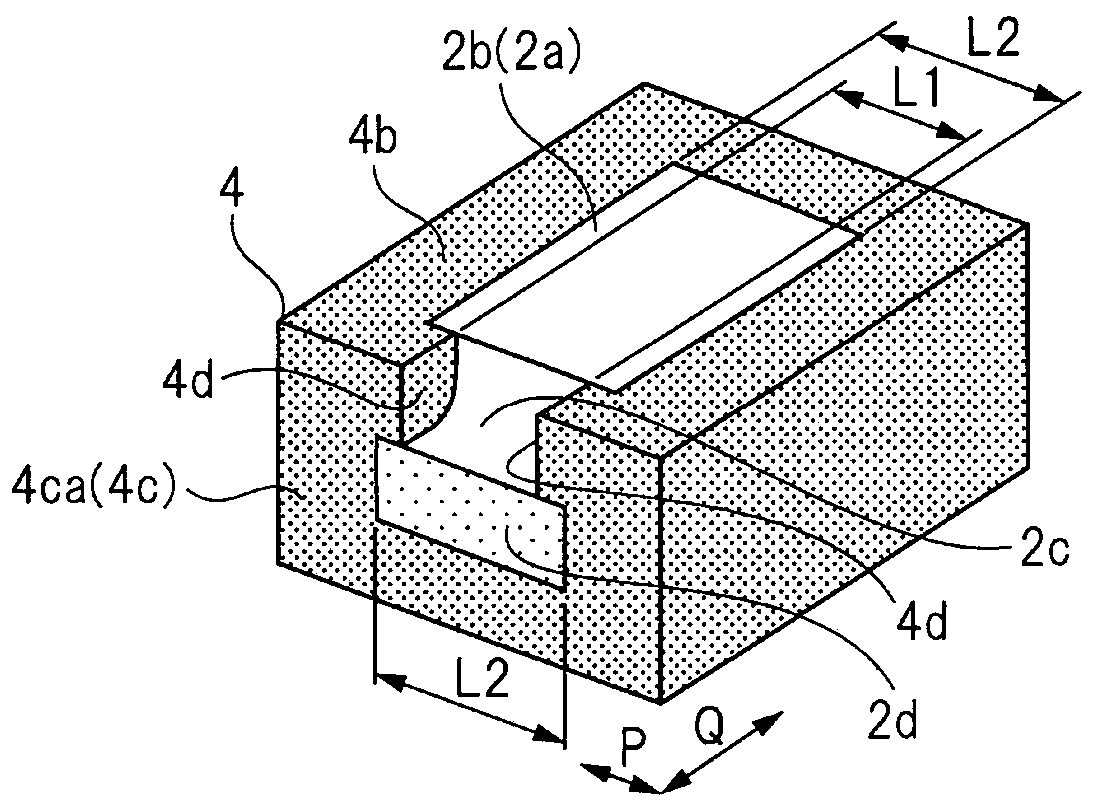

[0080] figure 1 It is a perspective view showing an example of the structure on the mounting surface side of the semiconductor device according to the embodiment of the present invention, figure 2 is showing figure 1 An enlarged partial perspective view of the structure of Part A.

[0081]

[0082] figure 1 The shown semiconductor device according to this embodiment is a leadless package assembled by the so-called MAP method in which the package is diced and singulated during assembly. In this embodiment, a description will be given using DFN (Dual-Flat No-leads: Dual-Flat No-leads) 6 as an example of a leadless package assembled by the above-mentioned MAP method. DFN6 is a semiconductor package in which a plurality of lead portions 2a are arranged along each of two opposing side surfaces 4ca of a sealing body 4 made of resin, and a terminal portion 2b of each lead portion 2a is arranged on the sealing body 4 as on the back 4b of the mounting surface.

[0083] The deta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com