Hash join operator acceleration method and system based on FPGA-DDR

An operator and connection key technology, applied in the field of hash connection operator acceleration methods and systems, can solve the problem that the scale and quantity of high-speed Block-RAM cannot meet the requirements of the number of large databases, so as to compensate for bandwidth problems, accelerate effects, and improve The effect of operating efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

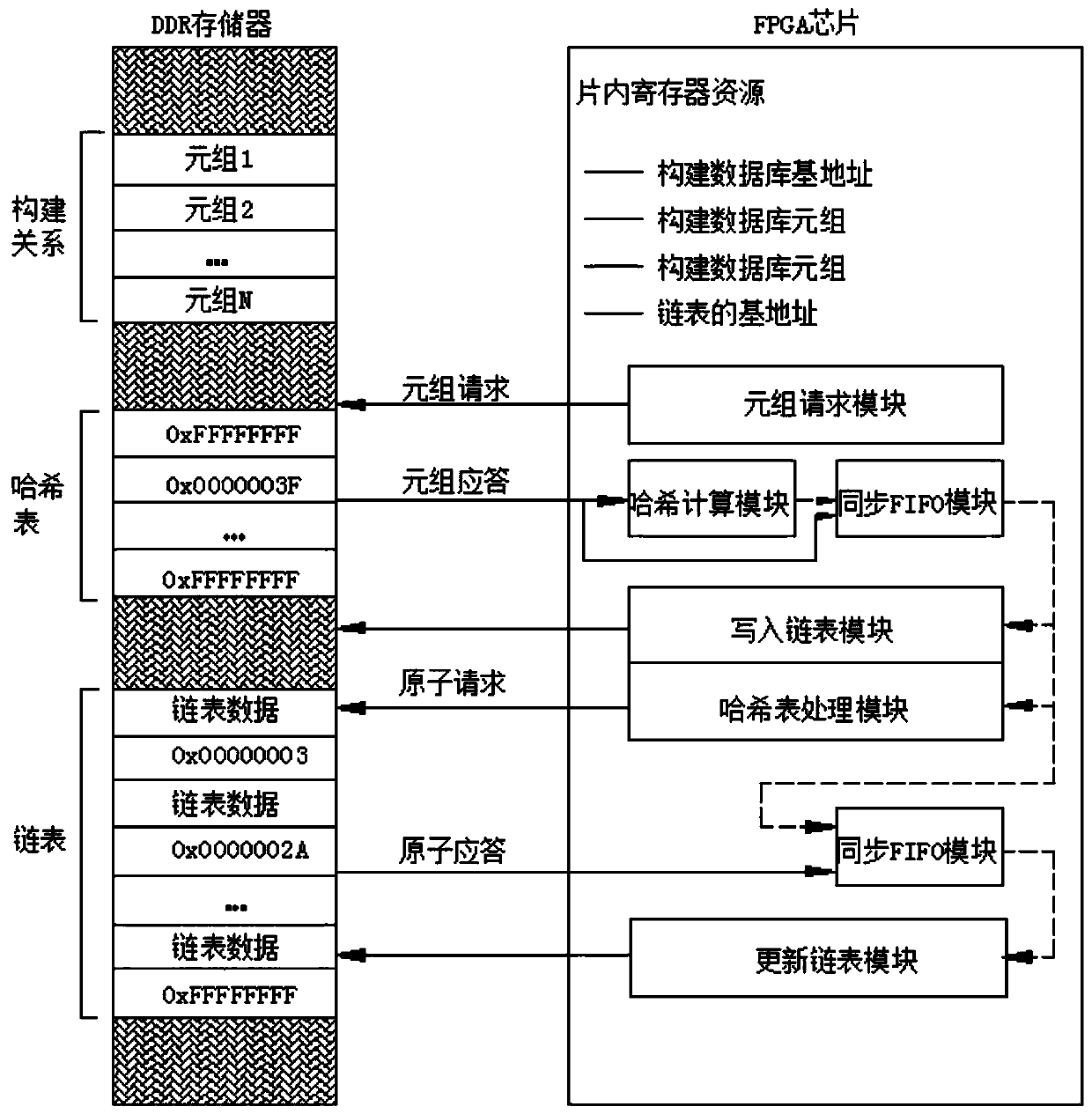

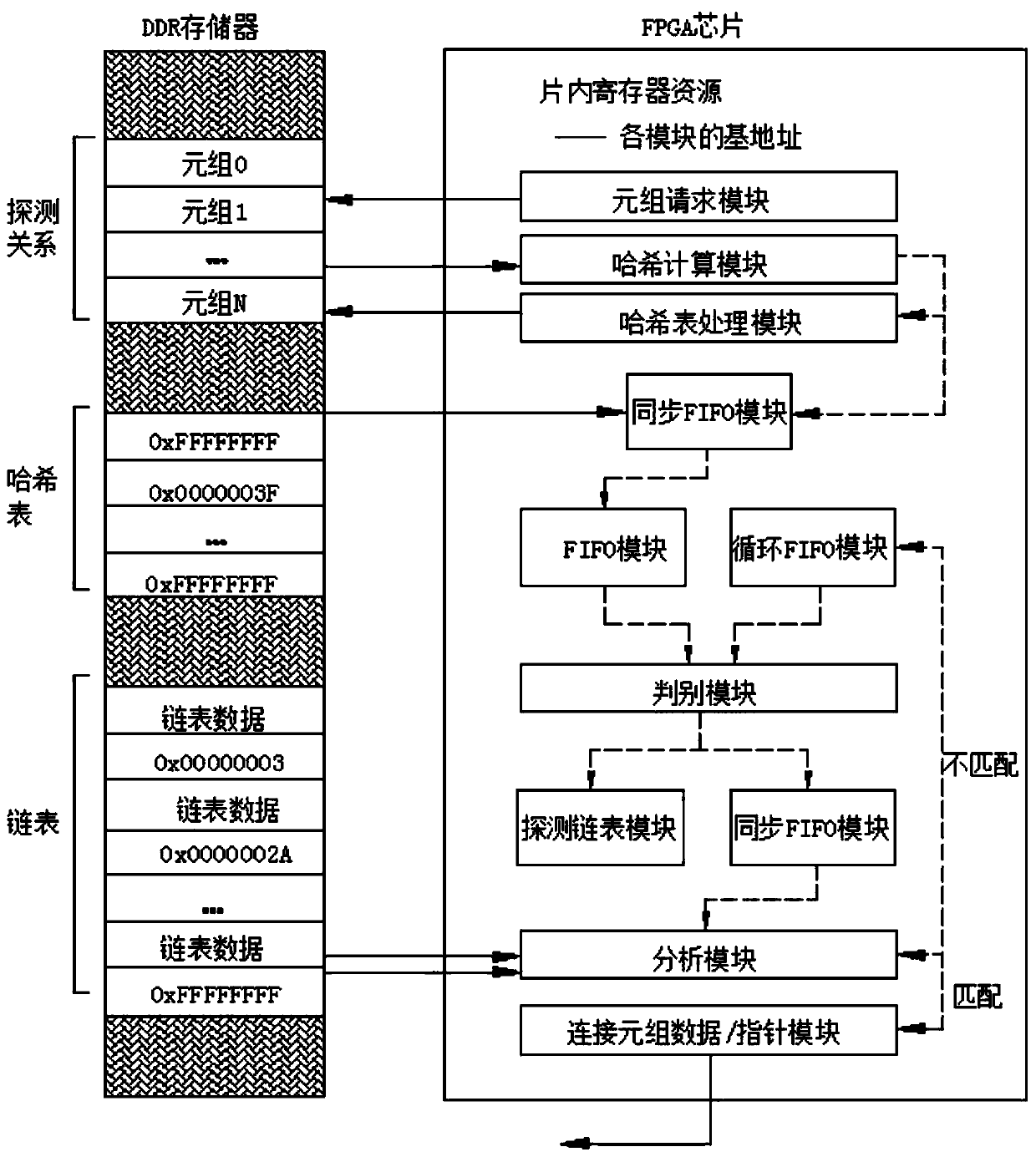

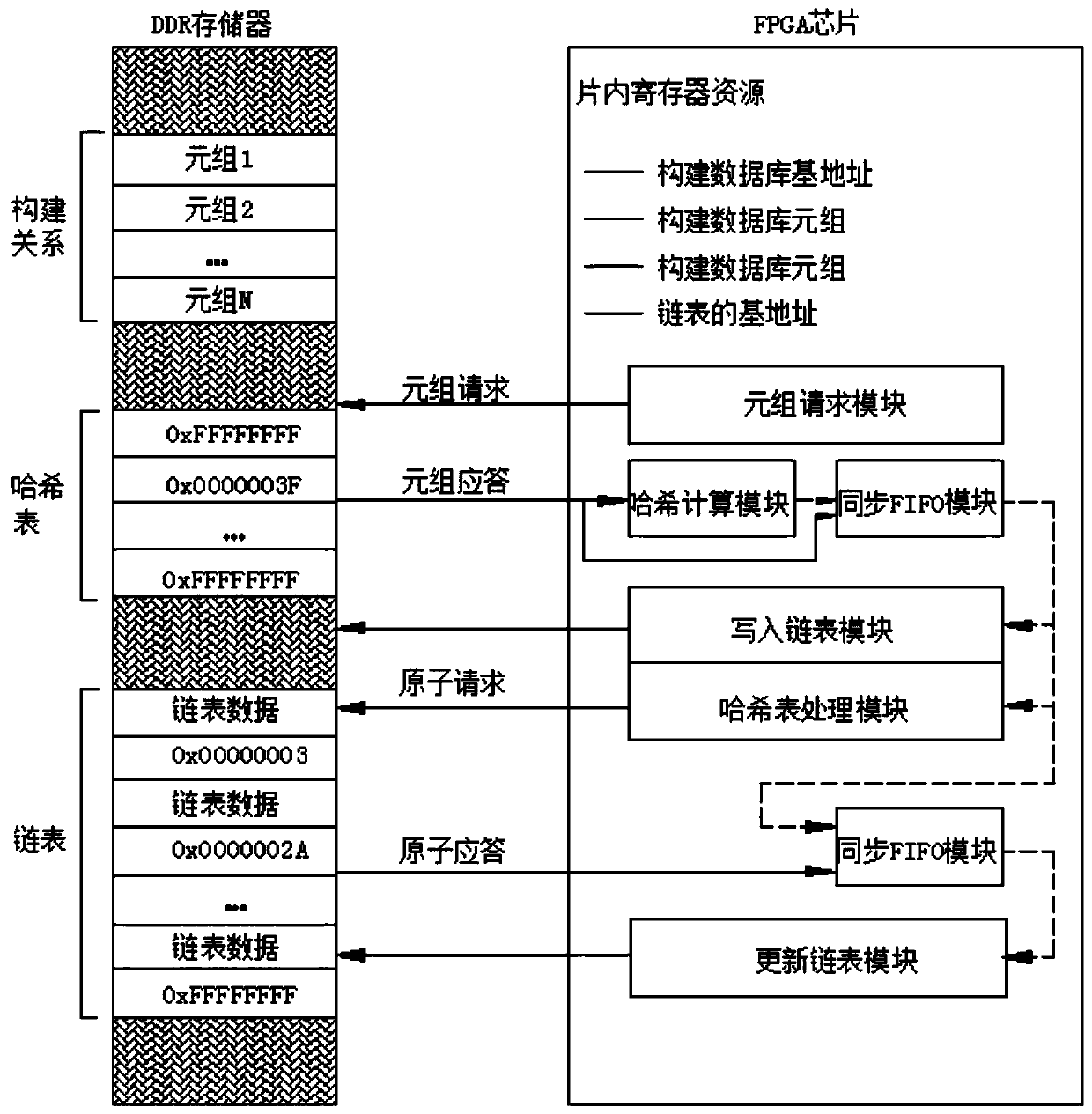

[0052] A kind of FPGA-DDR-based hash connection operator acceleration method of the present invention, DDR memory is an external memory, stores tuple, hash table and linked list through DDR memory; FPGA chip is configured with on-chip register, tuple request module, Hash calculation module, write link list module, hash table processing module, update link list module, detection link list module, judgment module, analysis module, connection tuple data / pointer module, FIFO module, synchronous FIFO module and loop FIFO module , wherein the on-chip register resources include the base address of the database, the base address of the database tuple, the base address of the hash table, the base address of the linked list, and the base addresses of the above-mentioned modules; under the cooperation of the above-mentioned DDR memory and the FPGA chip, through The construction phase and detection phase of the hash connection execute parallel multi-thread operations to realize the constru...

Embodiment 2

[0085] The hash connection operator acceleration system based on FPGA-DDR of the present invention includes a DDR memory and an FPGA chip, and the DDR memory is used to store tuples, hash tables and linked lists, and the tuples include constructing tuples and detecting tuples, and hashing The table stores the head node of each linked list, and the connection keys with the same hash value belong to the same hash bucket, and the elements in each hash bucket are linked through a linked list;

[0086] The FPGA chip is configured with the following modules:

[0087] A tuple request module that builds a thread for each tuple and generates a request for its join key;

[0088] Hash calculation module, used to calculate the hash value of the connection key;

[0089] Write the linked list module, which is used to write the connection key key value and tuple pointer into the new node of the corresponding hash bucket linked list;

[0090] The hash table processing module is used to gene...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com