A universal convolutional neural network accelerator based on a one-dimensional pulsation array

A technology of convolutional neural network and systolic array, which is applied in the field of electronic information and deep learning, can solve the problems of large amount of parameters and calculation, and achieve the effects of improving operating efficiency, reducing communication waiting time, and improving computing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The technical solutions and beneficial effects of the present invention will be described in detail below in conjunction with the accompanying drawings.

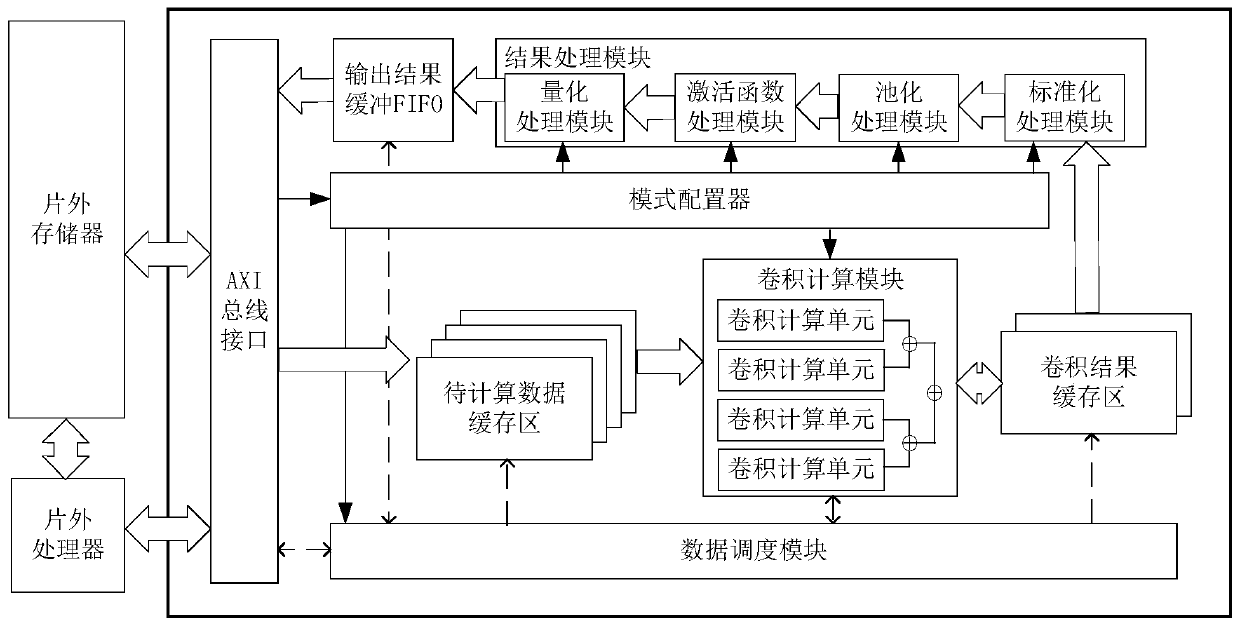

[0025] Such as figure 1 The structure of each module of the accelerator designed by the present invention is shown, and the working method is as follows:

[0026] The off-chip processor sends a mode configuration instruction to the accelerator in advance, and the mode configurator decodes the instruction after receiving the instruction, and accordingly sets the configuration port of each functional module or assigns a value to the configuration register. The configurable part of the data scheduling module includes feature map row length ML, convolution kernel row number KH, convolution kernel column number KL, convolution kernel step size S, convolution kernel number KC, feature map filling number PAD, single channel Calculate the number of rows LC, pool type PT, data update mode DR these configuration registers. When the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com