A cache partition division method for a reconfigurable system

A cache partition and system reconstruction technology, applied in general-purpose stored program computers, architectures with a single central processor, etc., can solve performance changes, affect throughput, reduce cache utilization, etc., to reduce bandwidth requirements and performance. Optimized, fine-tuned effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

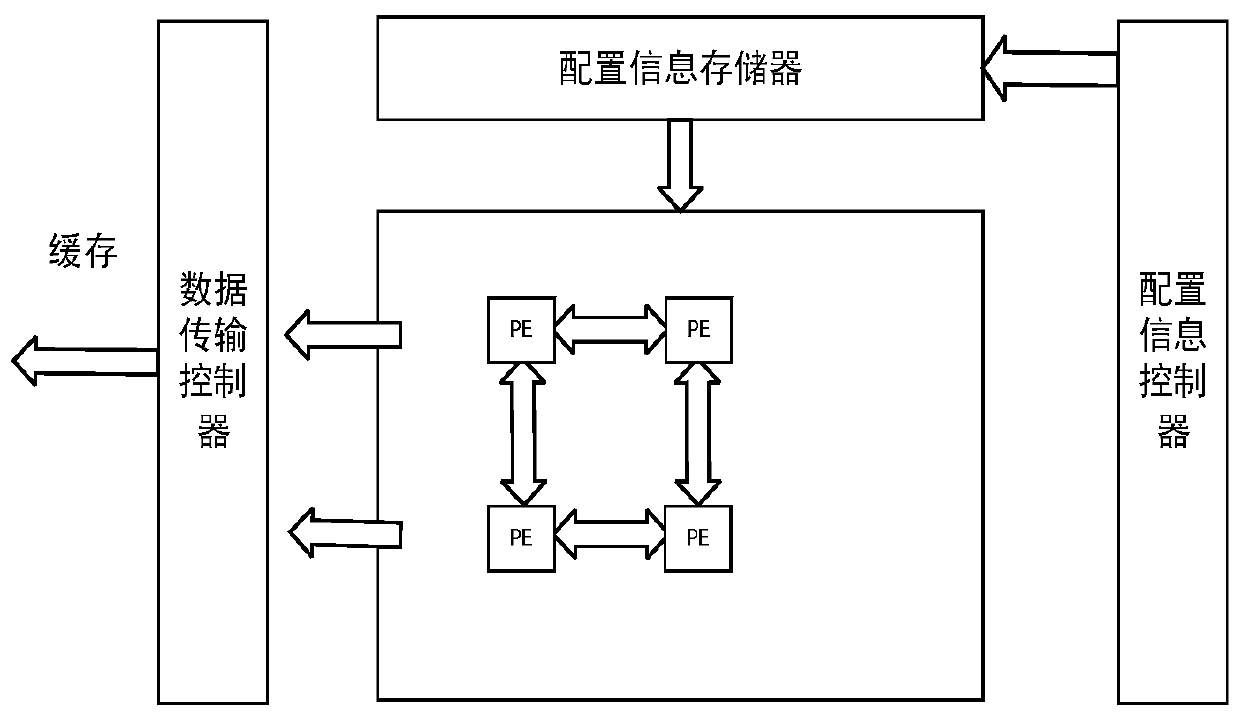

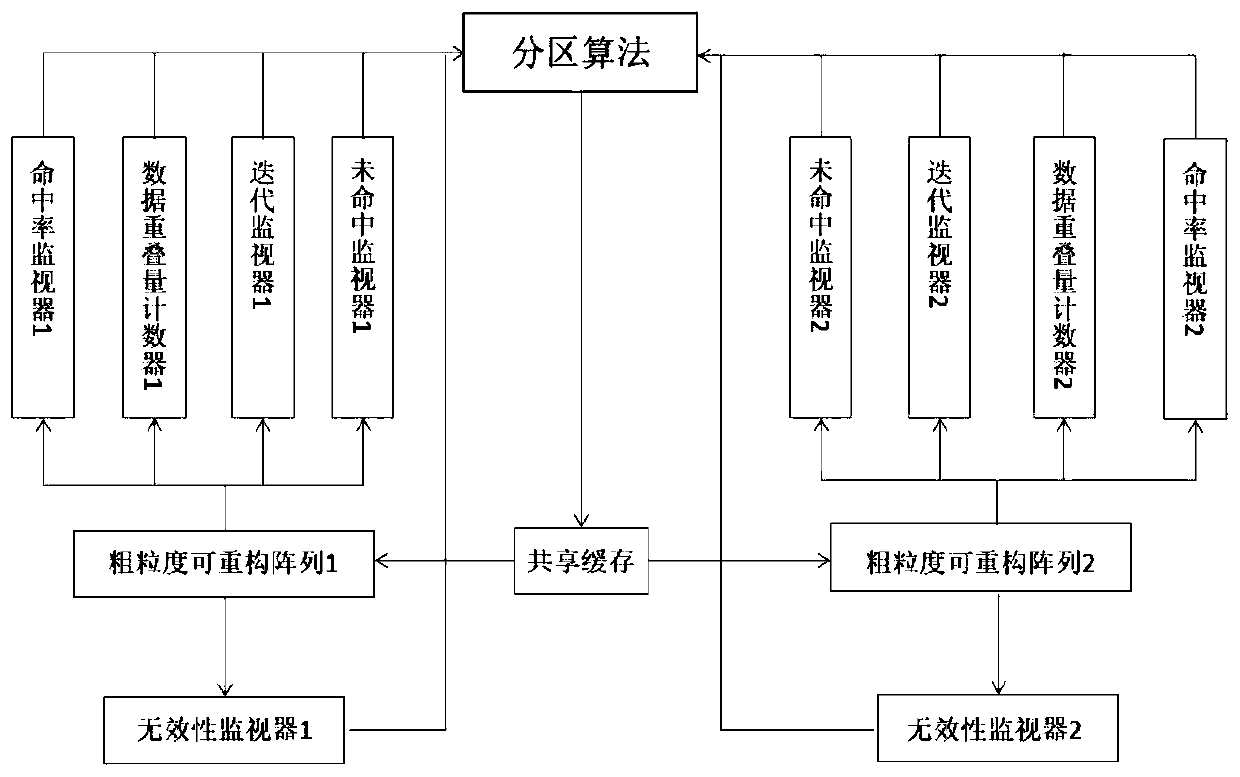

[0053] main feature:

[0054] 1. Utilization-based partitioning method (Utility-BasedCache Partitioning) and invalid scaling (Futility Scaling), reasonably divide the cache area.

[0055] 2. Introduce two new data - the amount of data overlap and the number of iterations, and the data can be tracked and calculated through the hardware.

[0056] The main advantage

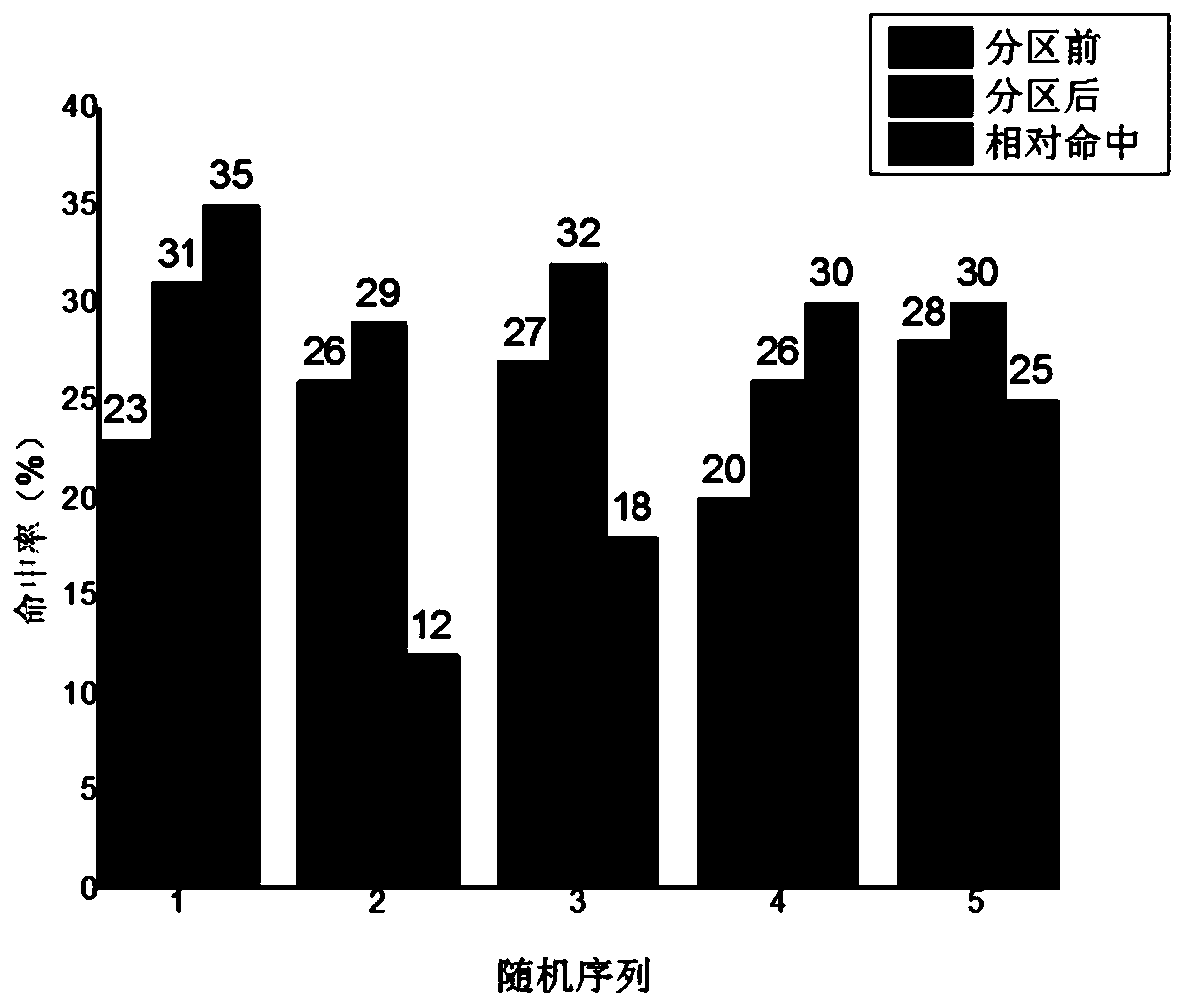

[0057] 1. Combining the advantages of Utility-Based Cache Partitioning and Utility Scaling, the cache area is divided reasonably, and the appropriate content in the main memory is placed in the appropriate cache partition to improve system performance.

[0058] 2. Correct the original cache division by using data overlap and iteration times to obtain a more reasonable scaling factor α and invalidity f, and accurately and meticulously control the partition size, so that partitions with high performance will allocate more cache resources, optimize performance.

[0059] The cache division method proposed by the presen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com