Memory and manufacturing method thereof

A manufacturing method and memory technology, applied in the direction of electric solid-state devices, semiconductor devices, electrical components, etc., can solve the problems of high process precision requirements and difficulty in controlling the production process of reducing parasitic capacitance, so as to achieve the reduction of process control precision requirements, parasitic capacitance, etc. The capacitance is easy to control and the effect of expanding the process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] As mentioned in the background technology section, the 3D NAND manufacturing process used in the prior art to reduce parasitic capacitance is difficult to control and requires high process precision.

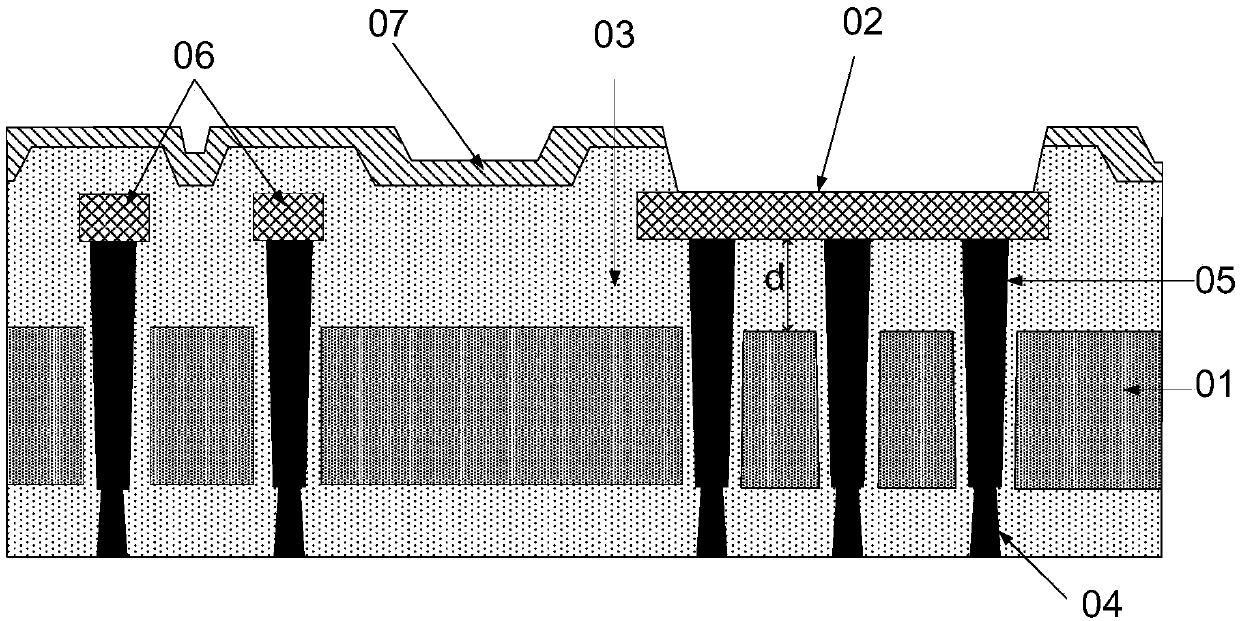

[0046] The invention finds that the reason for the above phenomenon is that please refer to figure 1 , figure 1 It is a schematic diagram of a cross-sectional structure of a memory; the memory includes a silicon substrate 01, an insulating layer 03 formed on both sides of the silicon substrate 01, a metal wiring 06 formed inside the silicon substrate 01, and a through-silicon contact part penetrating the substrate (through silicon contact, TSC) 05 , and a through array contact (TAC) 04 electrically connected to the TSC 05 , and a protective layer 07 is also provided on the surface of the memory structure. Wherein, a metal pad 02 is formed in a part of the protective layer 07, and the metal pad 02 is used to connect the circuit inside the memory to the chip.

[0047] Whe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com