A method and a system for upgrading a CPLD based on Whitley platform

A platform and high-level technology, applied in the field of server communication, can solve the problem of insufficient stability of CPLD upgrade, achieve the effect of avoiding unstable performance and improving stability and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

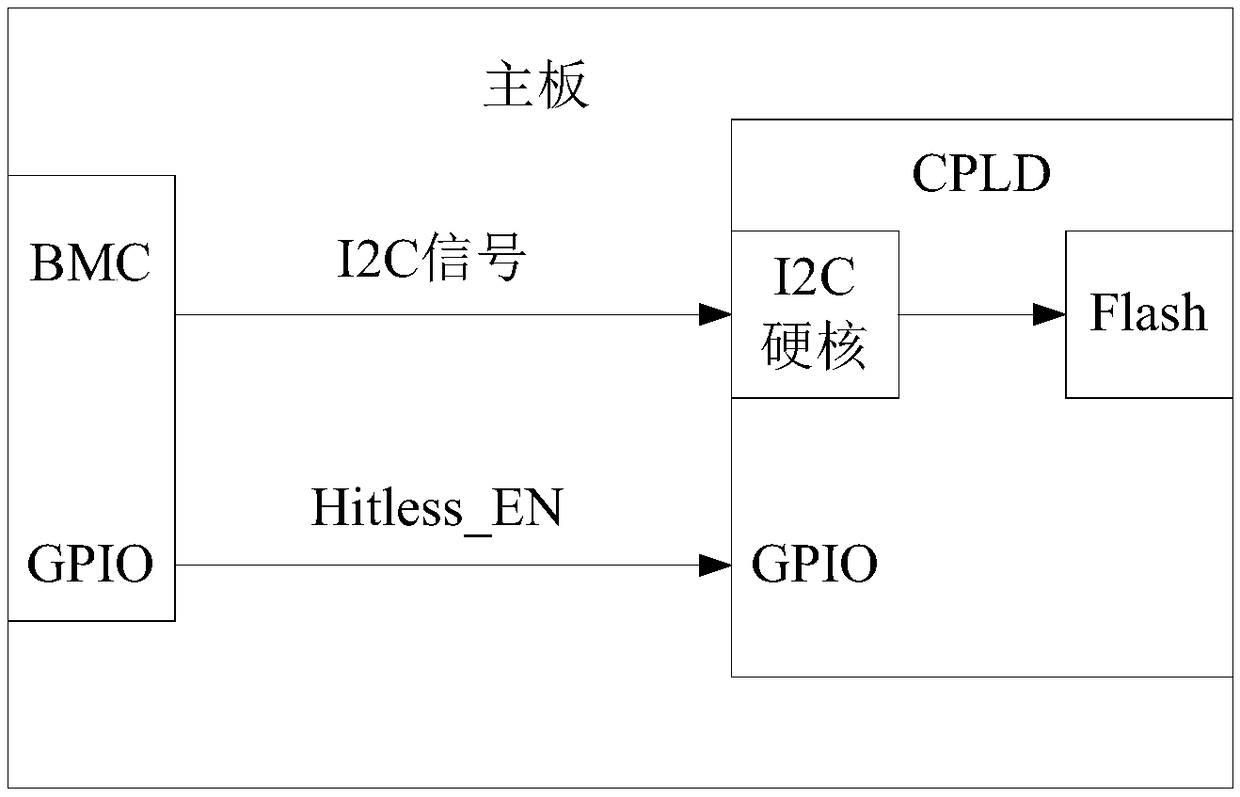

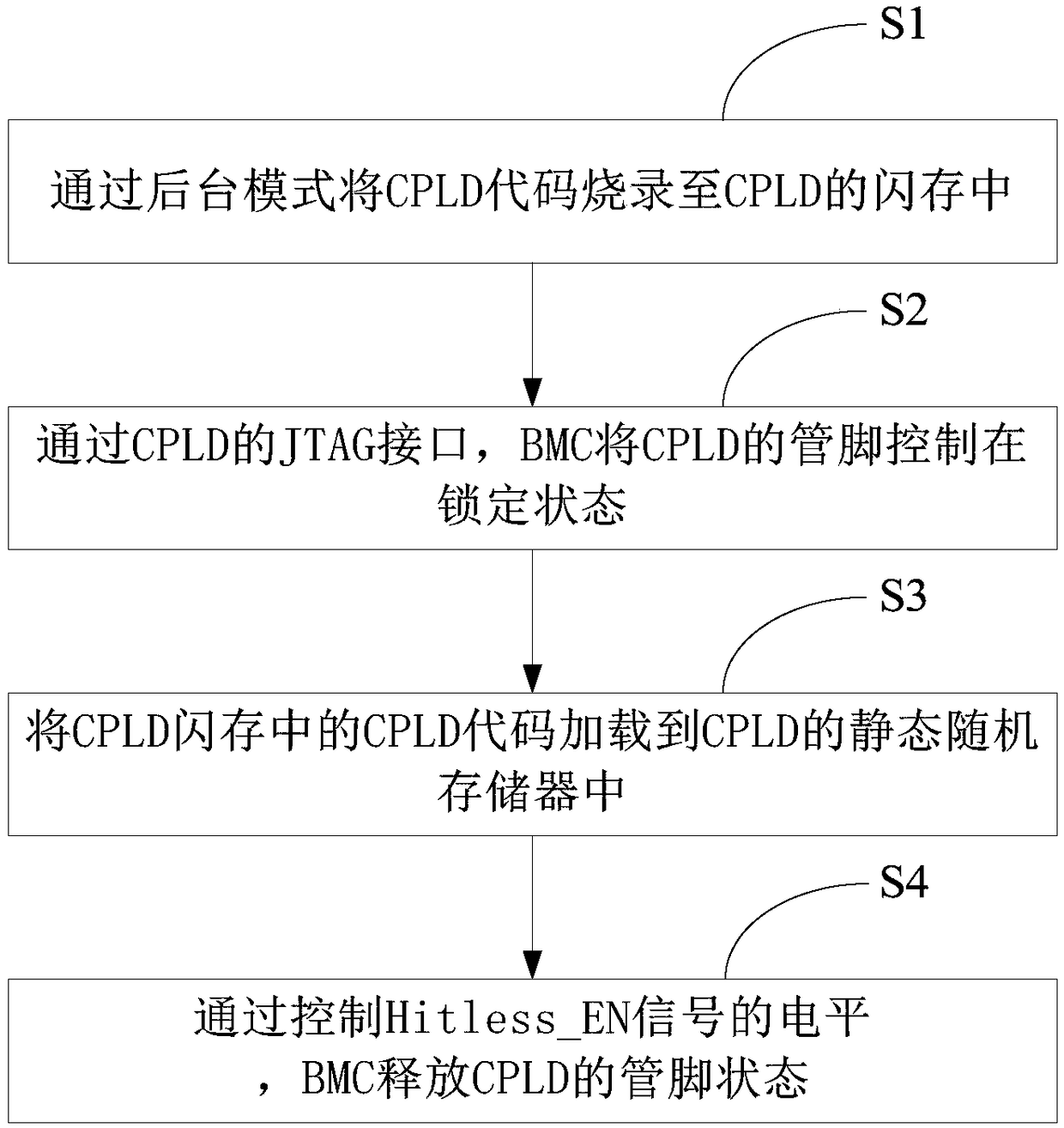

[0066] see image 3 , image 3 It is a schematic flowchart of a method for upgrading a CPLD based on the Whitley platform provided by the embodiment of the present application. Depend on image 3 As can be seen, the method in this embodiment mainly includes the following steps:

[0067] S1: Burn the CPLD code into the flash memory of the CPLD through the background mode.

[0068] Specifically, the BMC uses the JTAG interface of the CPLD to burn the code of the built-in flash memory of the CPLD through the background mode, and burns the code of the CPLD that needs to be upgraded into the Flash of the CPLD. When programming, the CPLD is in the normal operation state, and the background programming mode is adopted, which will not affect the normal operation of the CPLD, and is conducive to improving the upgrading efficiency of the CPLD.

[0069] S2: Through the JTAG interface of the CPLD, the BMC controls the pins of the CPLD to be locked.

[0070] After the BMC burns the CP...

Embodiment 2

[0106] exist Figure 3-Figure 5c On the basis of the illustrated embodiment see Figure 6 , Figure 6 It is a schematic structural diagram of a system for implementing CPLD upgrade based on the Whitley platform provided by the embodiment of the present application. Depend on Figure 6 It can be seen that the system for implementing CPLD upgrade based on the Whitley platform in this embodiment mainly includes four parts: a programming module, a first locking module, a loading module and a releasing module. Among them, the burning module is used to burn the CPLD code into the flash memory of the CPLD through the background mode; the first locking module is used to control the pins of the CPLD in a locked state through the JTAG interface of the CPLD; the loading module is used to flash the CPLD The CPLD code in is loaded into the SRAM of the CPLD; the release module is used to release the pin state of the CPLD by controlling the level of the Hitless_EN signal, and the Hitless_...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com