Fin field effect transistor forming method and semiconductor structure

A technology of fin field effect transistors and fins, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., and can solve problems such as complex processes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] It can be seen from the background art that the process of forming the fin field effect transistor in the prior art is complicated.

[0033] With the development of devices toward miniaturization and miniaturization, the forming process of FinFET becomes more and more complicated, especially the process steps of forming the fins in FinFET become more and more cumbersome.

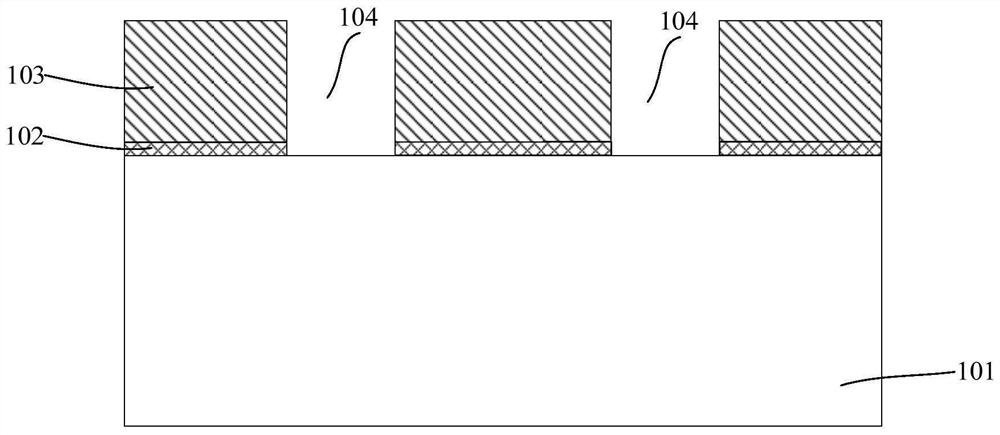

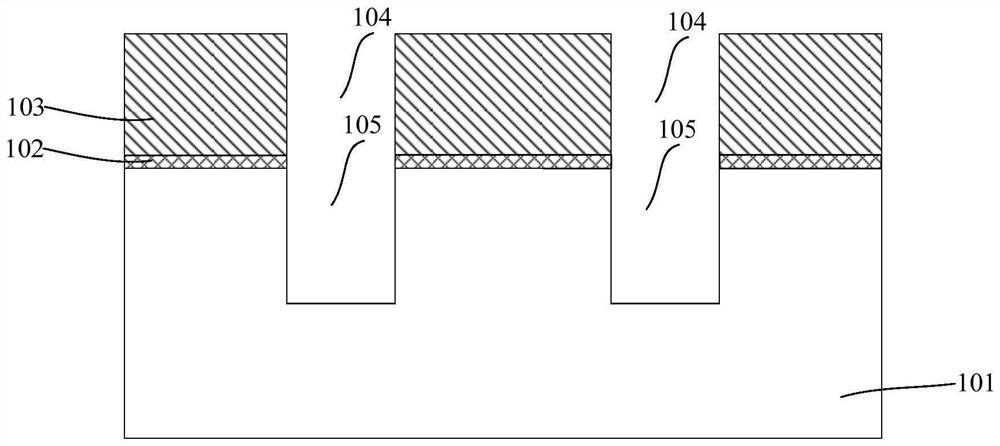

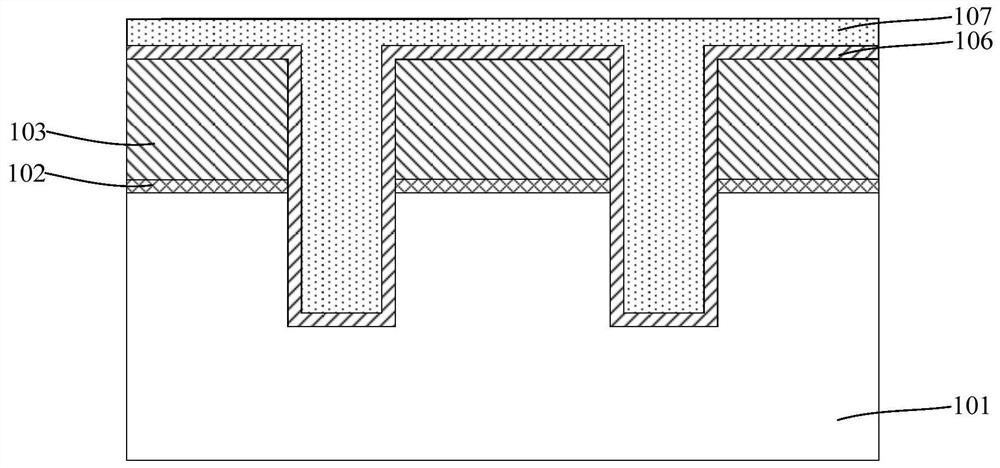

[0034] In order to solve the above problems, the present invention provides a method for forming a fin field effect transistor, comprising: providing a substrate; forming a mask layer on the substrate, the mask layer having a first opening exposing the substrate ; using the mask layer as a mask, etch and remove the base of the first thickness along the first opening, forming a second opening in the base; filling the cores in the first opening and the second opening layer; remove the mask layer to expose part of the core layer sidewalls; form sidewalls on the exposed core layer sidewalls and part of th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com