Network and hierarchical routing constructs with heterogeneous memory structures for scalable event-driven computing systems

A driver and event technology, applied in transmission systems, biological neural network models, electrical components, etc., can solve problems such as limiting the space of network connection solutions, maximize network programmability or/and flexibility, minimize memory requirements or / and delayed effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

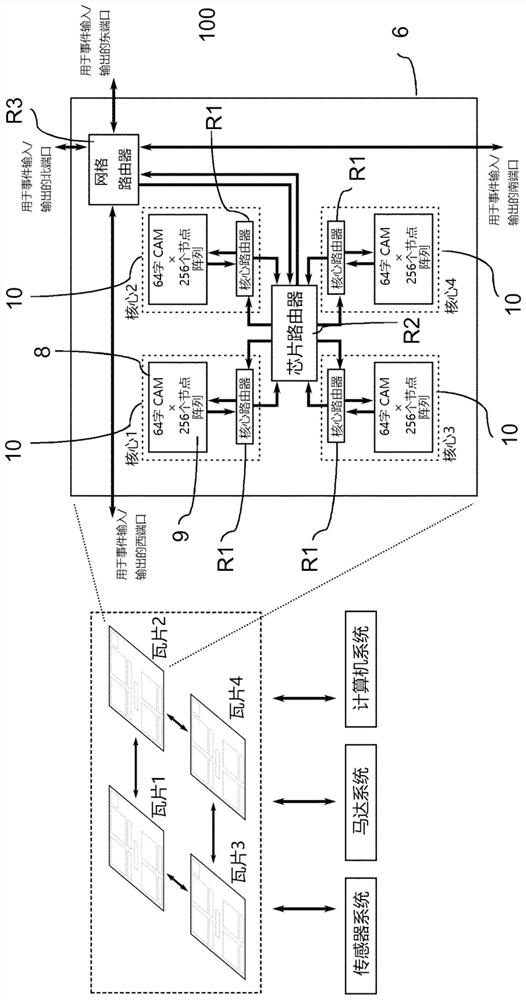

[0064] Embodiments of the present invention provide a VLSI (Very Large Scale Integration, Very Large Scale Integration) with a distributed memory and a heterogeneous memory structure for a scalable neural network, which can implement an event-driven neural architecture. The hierarchical router architecture provides a power and time efficient strategy for interconnecting nodes within and between multiple cores distributed on a multicore chip. Distributed memory in the cores and events broadcast in each core provide a large fan-out to enable large neural networks with structural constraints typical of biologically possible models. Fully asynchronous router and programming constructs allow fast operations of synaptic computations for upcoming offline learning.

[0065] The terms neuron and synapse as used herein represent electrical circuits that mimic biological neurons and synapses. Electronic neurons sum up the contributions of associated synapses to generate spike events. N...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com