Array substrate and manufacturing method

A technology of an array substrate and a manufacturing method, which is applied in the field of liquid crystal display panels, can solve problems such as increased parasitic capacitance, abnormal splash screen, wrong writing of signals, etc., and achieves reduction of area, improvement of aperture ratio, and constant resistance of resistance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

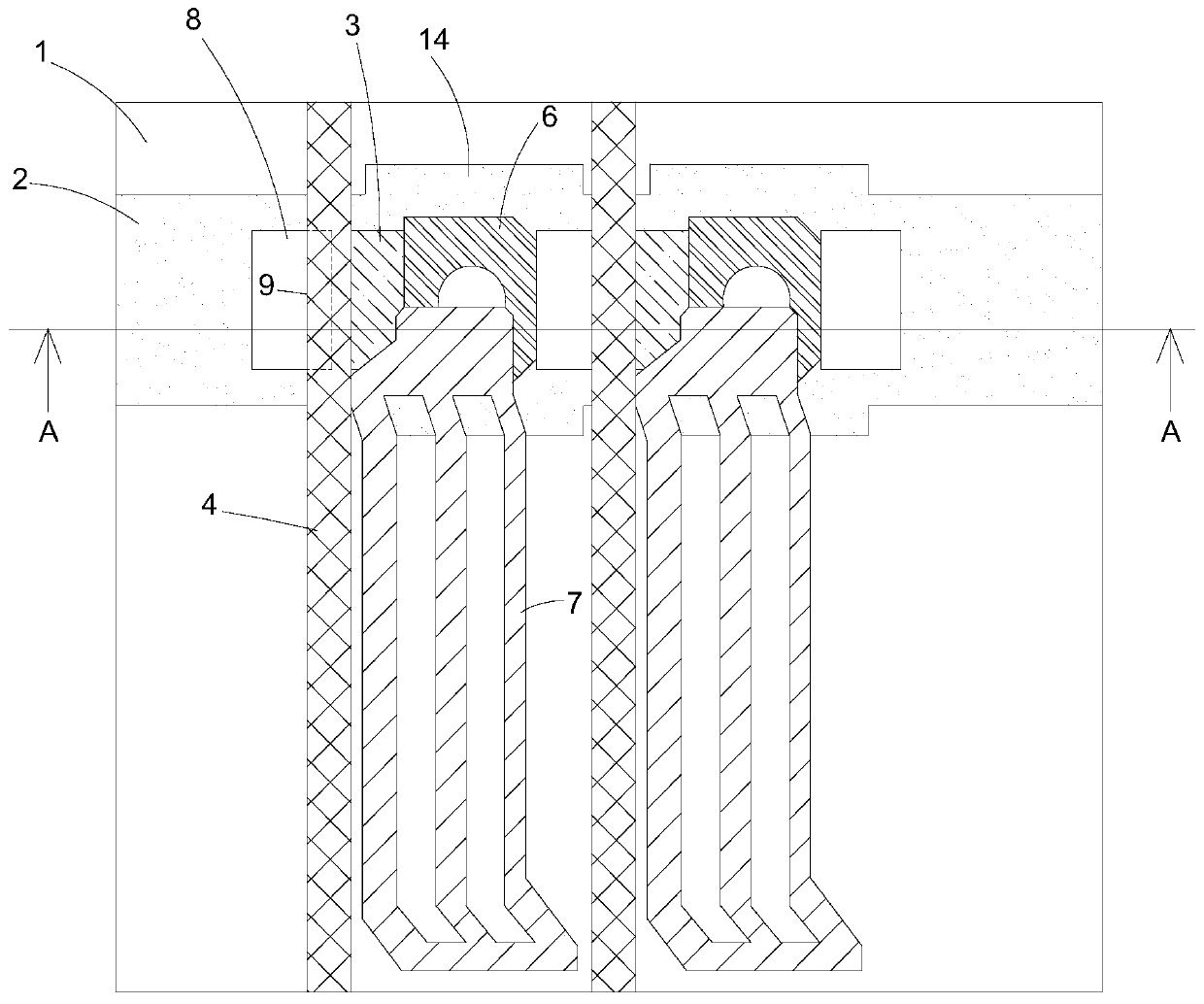

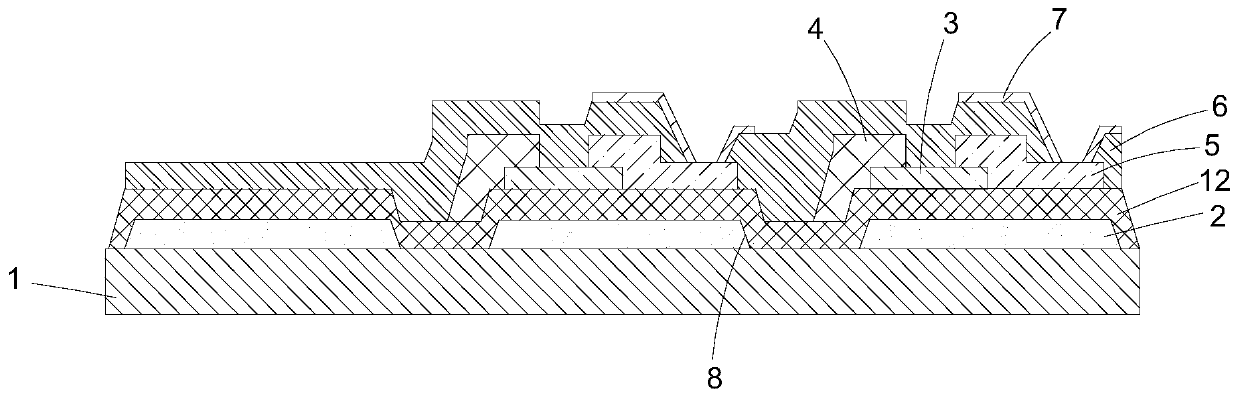

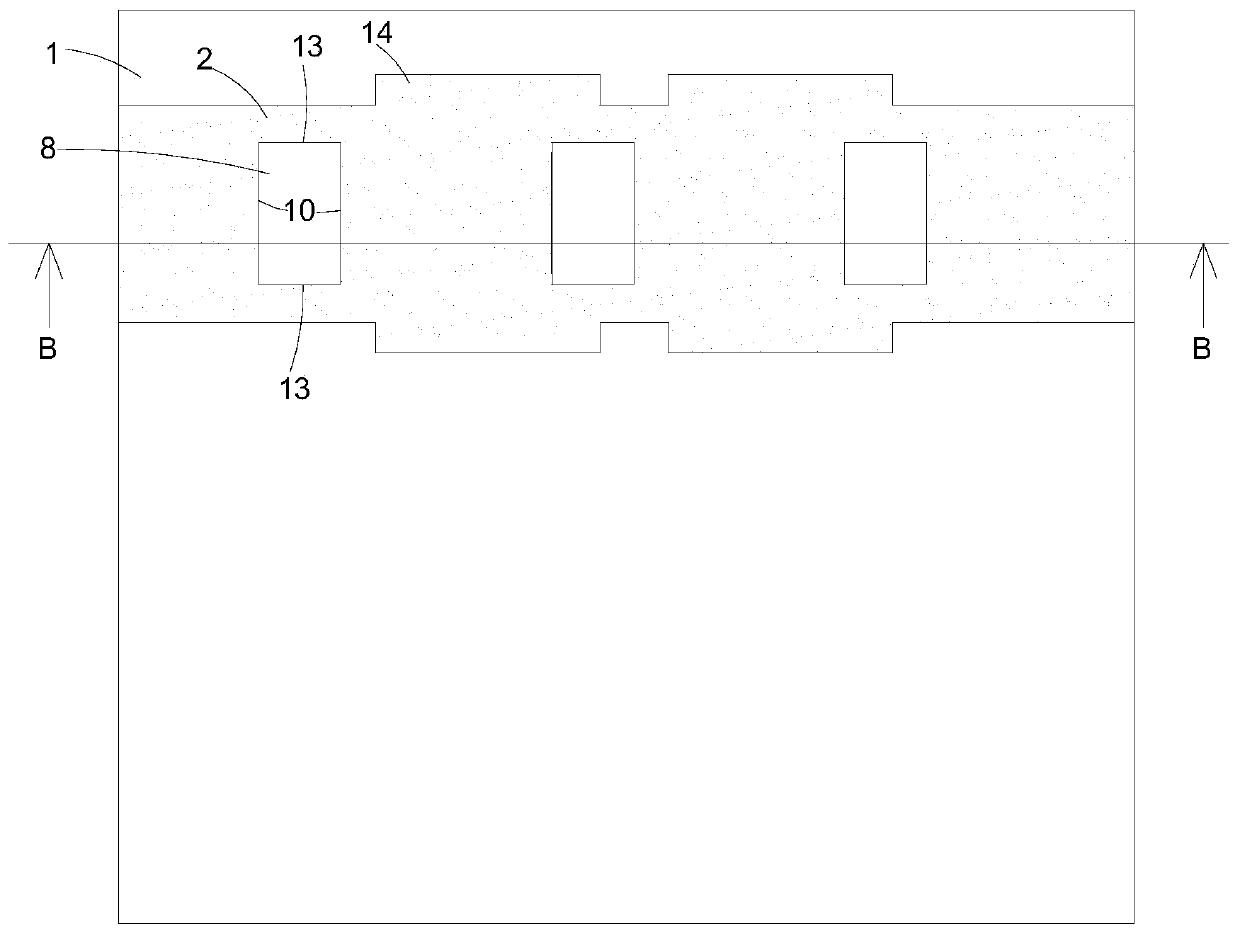

[0035] exist Picture 1-1 , 2-1 , 3-1, 4-1, and 5-1 only show the positional relationship of devices related to the present invention.

[0036] Such as Picture 1-1 and Figure 1-2 As shown, an array substrate of the present invention includes a substrate 1, a plurality of scanning lines (gate lines) 2, an active layer 3 arranged on the scanning lines 2, and a plurality of data lines interlaced with the scanning lines 2 4. The drain electrode 5 in contact with the active layer 3, the passivation layer 6 formed on the drain electrode 5, and the pixel electrode 7 formed on the passivation layer 6; between the scanning line 2 and the active layer 3, a Layer gate insulating layer 12, the pixel electrode 7 is connected to the drain electrode 5 through the via hole on the passivation layer 6; scanning line holes 8 are respectively opened at the po...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com