Method for improving chip simultaneous testing number

A technology of simultaneous measurement of chips and chips, which is applied in the field of improving chip simultaneous measurement, can solve problems such as inability to effectively save test time, inability to realize simultaneous testing of multiple chips, production costs and process waste, and achieve the effect of improving test coverage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the purpose, technical solution and advantages of the present invention clearer, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings.

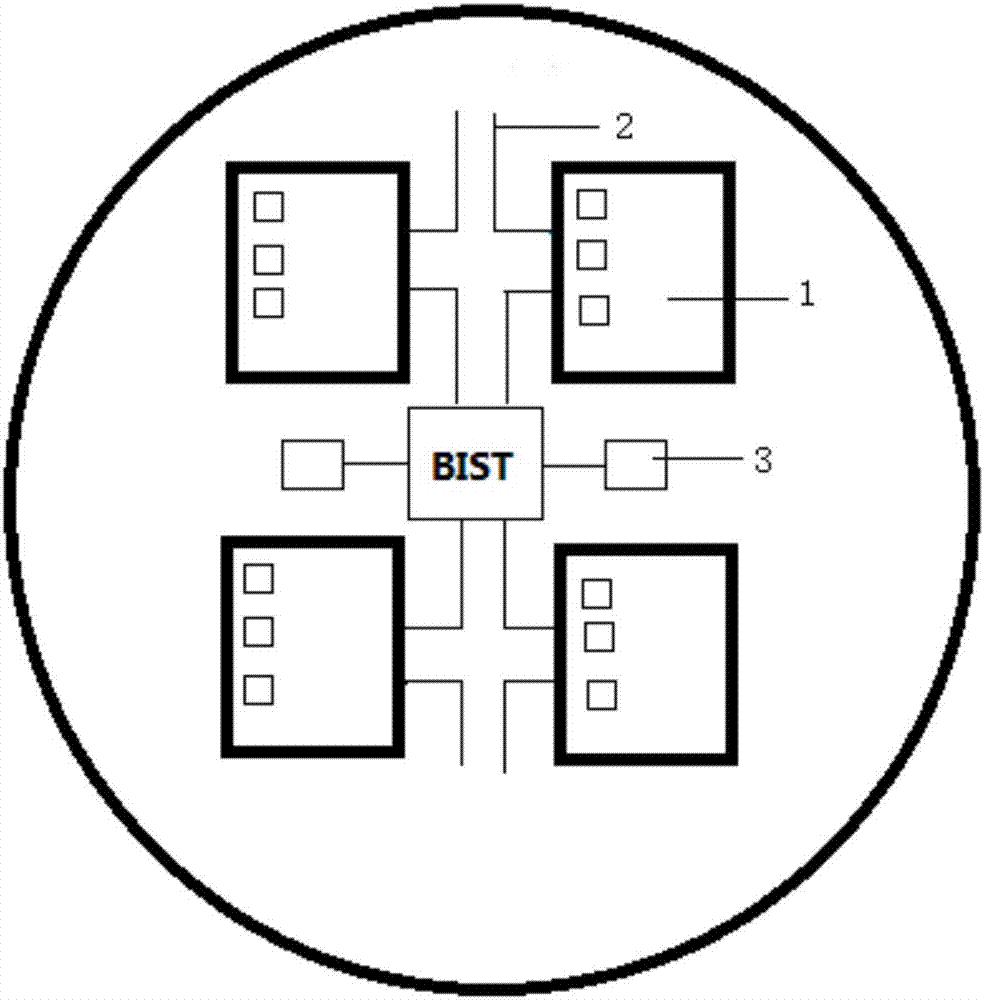

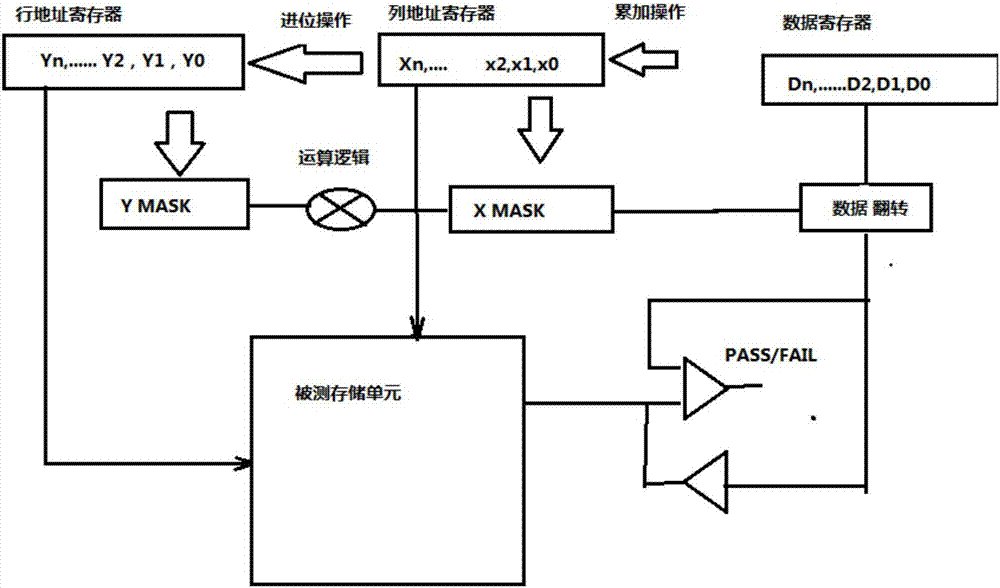

[0026] A method for improving the number of simultaneous chip measurements. The main innovations are as follows: (1) Use the position of the dicing groove to establish a BIST circuit. After the test is completed, the BIST circuit is cut off during the silicon wafer cutting and picking process, which does not occupy the chip area. It will not cause leakage of circuit information; (2) The BIST circuit is connected to multiple chips through the internal data bus, and an independent test control unit is set for each chip in the BIST circuit to realize multi-chip simultaneous testing; (3) The chip carries out the test of the relevant test pattern, realizes the full coverage test of the large-capacity memory in the tested chip, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com