Semiconductor layout structure

A layout structure, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, transistors, etc., can solve the problems of increasing the complexity of the manufacturing process and the cost of the manufacturing process, and reduce the complexity of the manufacturing process, reduce the manufacturing cost, The effect of simplifying pattern design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

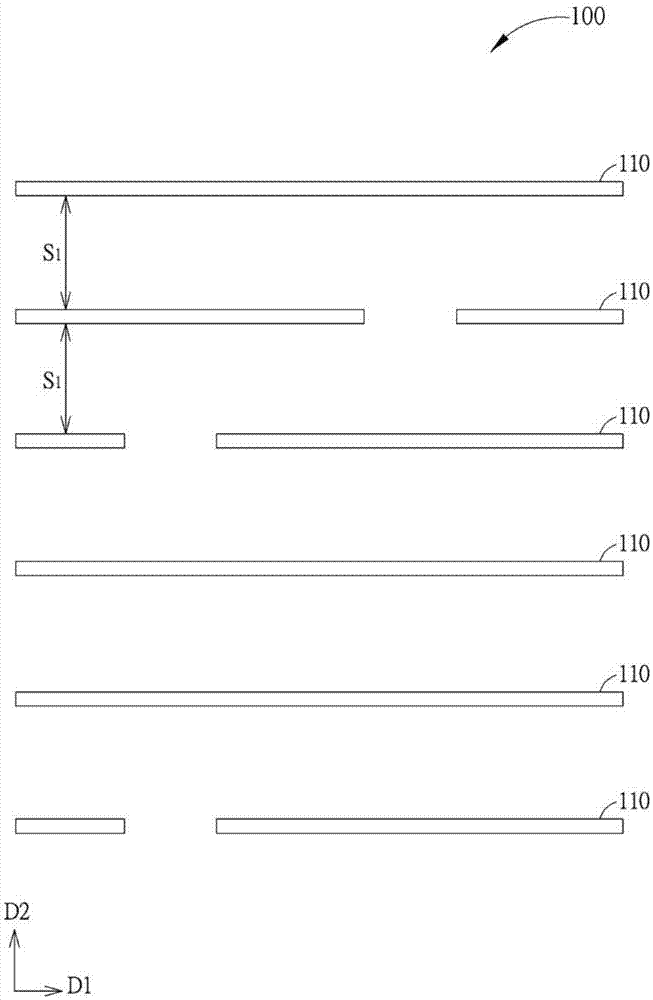

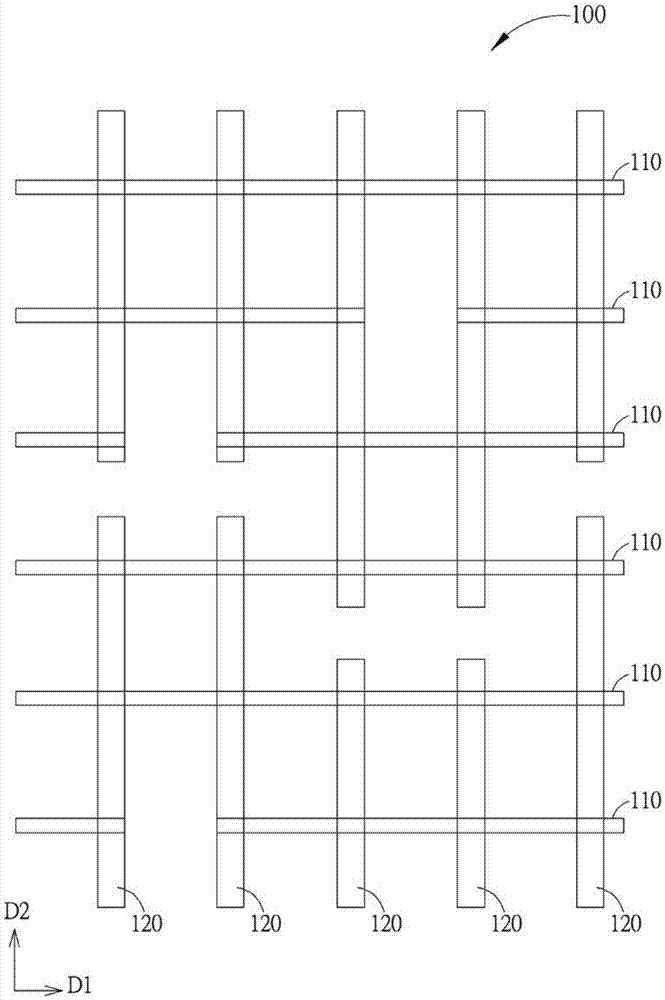

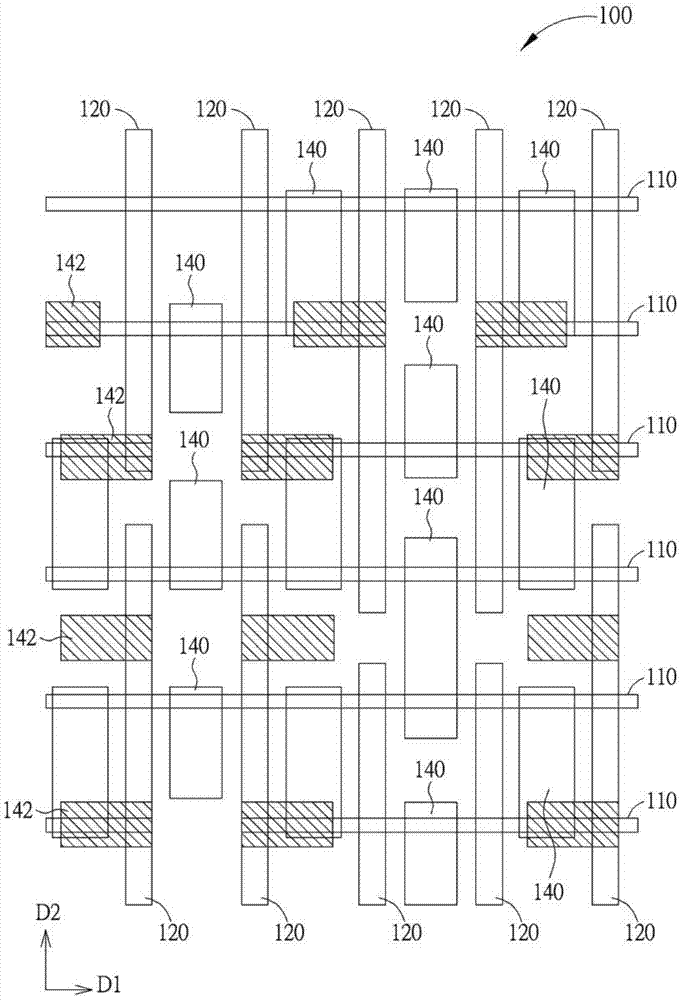

[0042] Persons familiar with this technology should understand that the following provides a number of different embodiments to disclose different features of the present invention, but not limited thereto. In addition, the drawings disclosed below are simplified to express the features of the present invention more clearly, so the drawings disclosed below do not show all the elements of a specified element (or device). In addition, the diagrams disclosed below are idealized schematic diagrams according to the present invention, so variations from these schematic diagrams, such as differences due to manufacturing techniques and or tolerances, are predictable. Therefore, the disclosure of the present invention should not be limited to the specific shapes disclosed in the following figures, but should also include deviations in shapes caused by manufacturing techniques.

[0043] In addition, those familiar with the technology should understand that in the following descriptions,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com