Vertical channel heterostructure field-effect transistor and preparation method thereof

A heterojunction field effect and vertical channel technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of high-voltage and high-temperature resistance, poor radiation resistance, and increased process complexity and other issues, to achieve the effect of simplifying the process difficulty, improving the yield rate, and improving the gate control ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

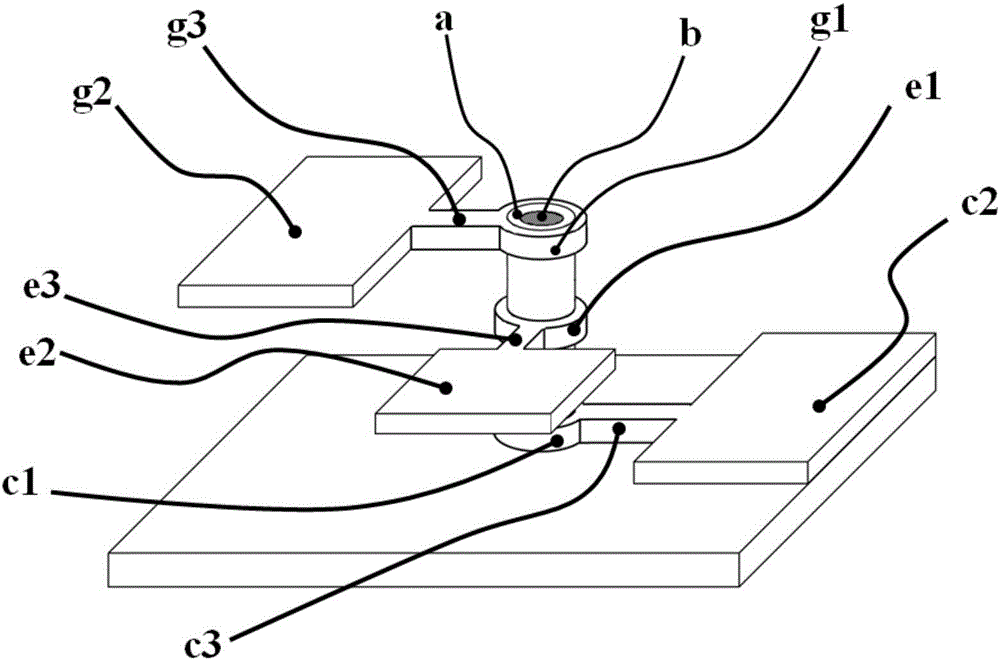

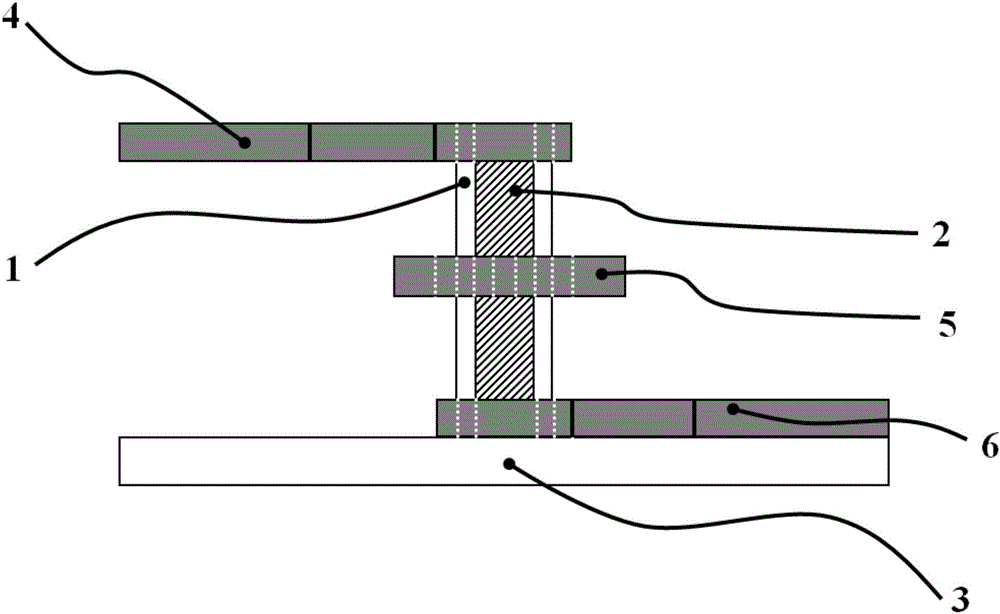

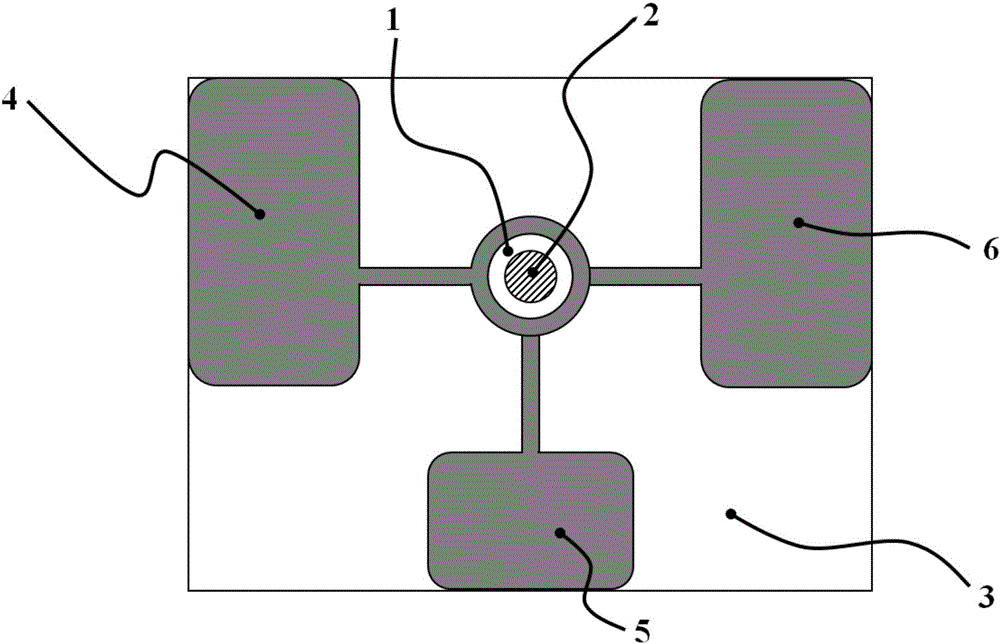

[0037] An aspect of the embodiments of the present invention provides a vertical channel-based heterojunction field effect transistor device (VC-HFET), which may include a source, a drain, a gate, and at least one heterojunction channel, so The axis of the heterojunction channel is substantially perpendicular to a selected plane, the heterojunction channel is located within a heterostructure including a second semiconductor and a first semiconductor disposed around the second semiconductor, the second semiconductor The forbidden band width of one semiconductor is larger than that of the second semiconductor, and two-dimensional electron gas (2DEG) or two-dimensional hole gas is formed in the heterojunction channel, and the source and drain are passed through the two-dimensional electron gas or two-dimensional hole gas. The two-dimensional holes are electrically connected, and the gate is distributed between the source and the drain.

[0038] The aforementioned "substantially p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com