Method of manufacturing micro LED chip with flip structure

A chip and flip-chip technology, applied in the field of fabrication of flip-chip microLED chips, can solve the problems of high cost, low yield, etc., and achieve the effects of high yield rate, high output efficiency, and good thermal conduction channels.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

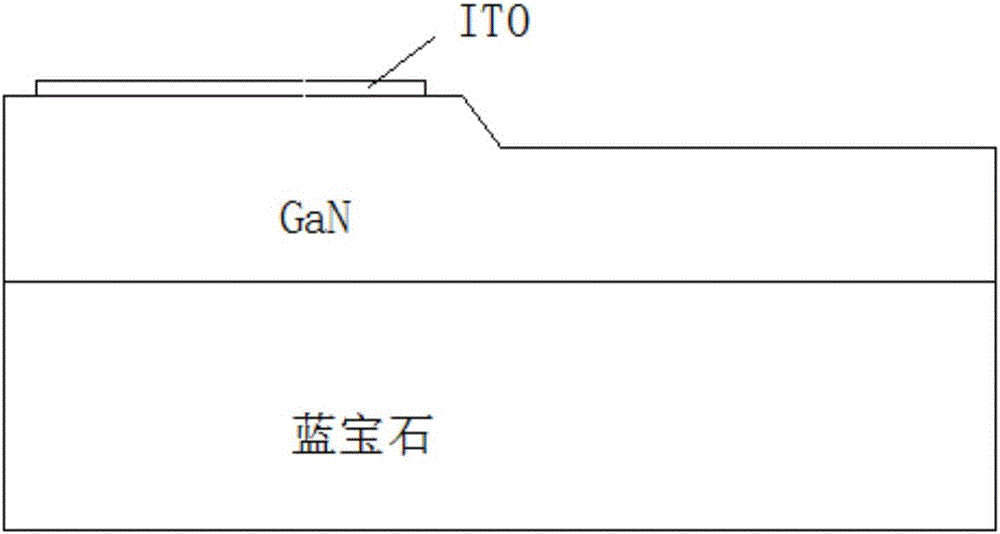

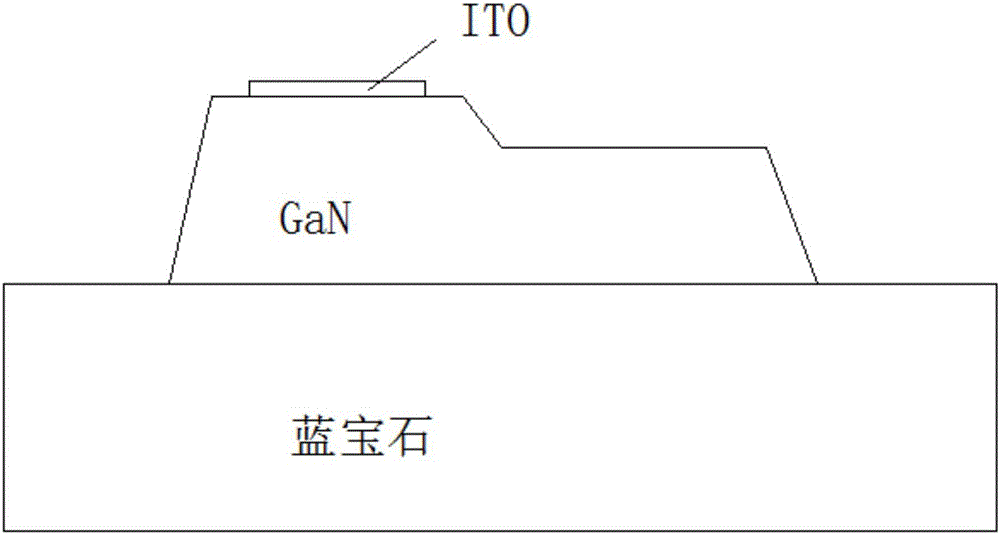

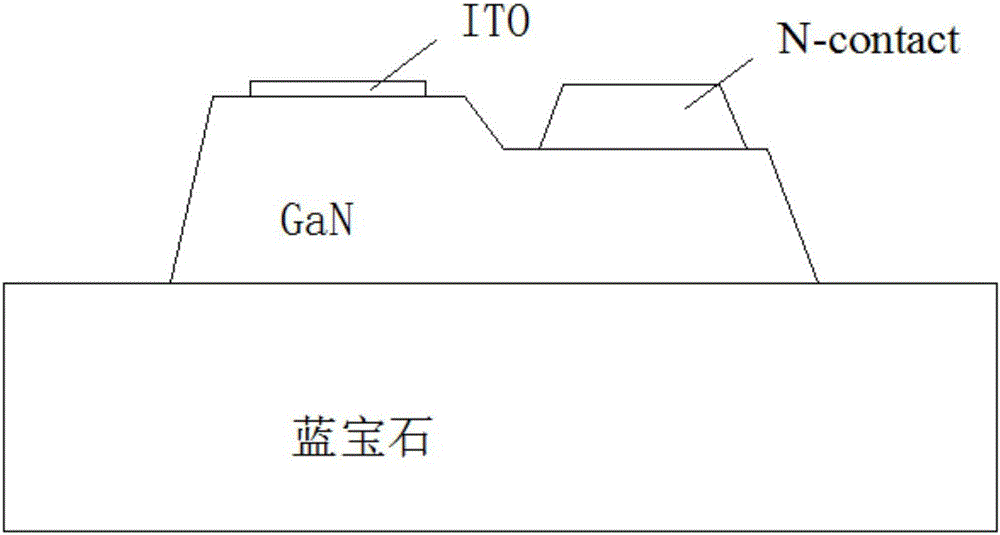

[0023] A method for preparing a micro LED chip with a flip-chip structure, comprising the following steps:

[0024] (1) Use a single-sided polished sapphire substrate to grow GaN epitaxy, and then grow an ITO film layer with a thickness of 20nm; then perform Mesa lithography and then Isolation lithography or first Isolation lithography and then Mesa lithography; single-sided polished sapphire substrate The thickness of the grown GaN epitaxy is 4 μm; the bare ITO film layer is etched after the Mesa pattern is etched, and the ICP etching is performed after the etching, and the etching depth is 1 μm to remove the photoresist; after Isolation photolithography ICP etching and removal of the photoresist, the surface Grown SiO 2 As a mask layer, the thickness is 1-2μm; after photolithography, use ICP dry etching to remove excess SiO 2 , etching gas optional SF 6 / CF 4 / CHF 3 ; use BCl afterwards 3 and Cl 2 Mixed gas etching GaN to Al 2 o 3 layer, remove photoresist, use HF / NH...

Embodiment 2

[0030] A method for preparing a micro LED chip with a flip-chip structure, comprising the following steps:

[0031] (1) Use a single-sided polished sapphire substrate to grow GaN epitaxy, and then grow an ITO film layer with a thickness of 100nm; then perform Mesa lithography and then Isolation lithography or first Isolation lithography and then Mesa lithography; single-sided polished sapphire substrate The thickness of GaN epitaxy growth is 8 μm; the exposed ITO film layer is etched after photolithography Mesa pattern, and ICP etching is performed after etching, and the etching depth is 2 μm to remove photoresist; after Isolation photolithography ICP etching and removal of photoresist, the surface Grown SiO 2 As a mask layer, the thickness is 2μm; use ICP dry etching after photolithography to remove excess SiO 2 , etching gas optional SF 6 / CF 4 / CHF 3 ; use BCl afterwards 3 and Cl 2 Mixed gas etching GaN to Al 2 o 3 layer, remove photoresist, use HF / NH 4 F mixed sol...

Embodiment 3

[0037] A method for preparing a micro LED chip with a flip-chip structure, comprising the following steps:

[0038](1) Use a single-sided polished sapphire substrate to grow GaN epitaxy, and then grow an ITO film layer with a thickness of 200nm; then perform Mesa lithography and then Isolation lithography or first Isolation lithography and then Mesa lithography; single-sided polished sapphire substrate The thickness of the grown GaN epitaxy is 10 μm; the exposed ITO film layer is etched after the Mesa pattern is etched, and the ICP etching is performed after the etching, and the etching depth is 3 μm to remove the photoresist; after Isolation photolithography ICP etching and removal of the photoresist, the surface Grown SiO 2 As a mask layer, the thickness is 1-2μm; after photolithography, use ICP dry etching to remove excess SiO 2 , etching gas optional SF 6 / CF 4 / CHF 3 ; use BCl afterwards 3 and Cl 2 Mixed gas etching GaN to Al 2 o 3 layer, remove photoresist, use H...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com