A Method of Low-Order Interleaving for Large-capacity Data Using FPGA

A data and cross-module technology, applied in the field of communication, to achieve the effect of reduced demand and strong access capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further described below in conjunction with accompanying drawing:

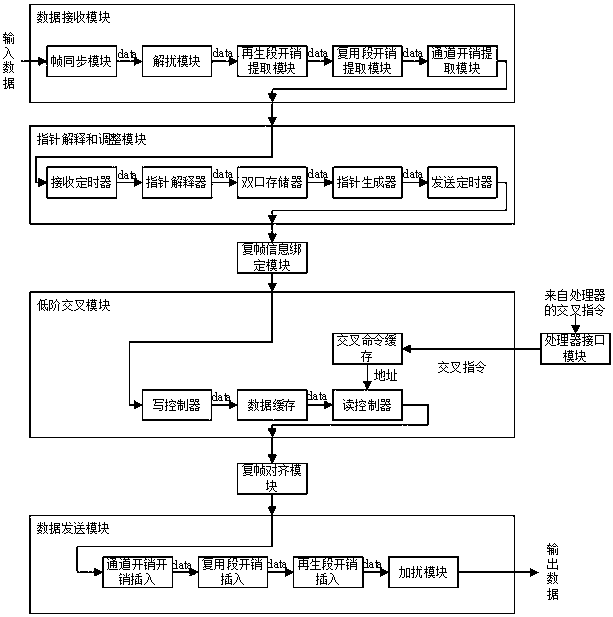

[0025] The working principle of FPGA (Field Programmable Gate Array) chip: refer to figure 1 , the chip function is divided into seven functional modules: data receiving module, pointer interpretation and adjustment module, multiframe information binding module, low-level crossover module, multiframe alignment module, processor interface module and data transmission module. Among them, the four modules of pointer interpretation and adjustment, multiframe information binding, low-level crossover, and multiframe alignment are the core modules in this solution, reflecting the idea of crossover first and then multiframe alignment. The three modules of data receiving, processor interface and data sending are conventional modules for processing SDH data, and the above seven modules complete the functions of the entire chip.

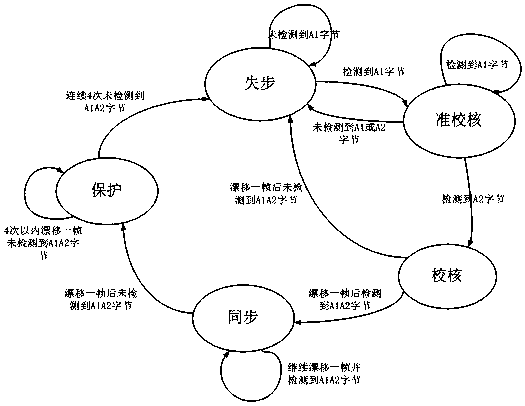

[0026] refer to figure 2 , The data receiving mod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com