Thin film transistor and manufacturing method and display panel

A technology of thin film transistors and manufacturing methods, applied in the direction of transistors, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve the problem of extending channel length and gate electrode length, deviating from the development trend of high-resolution displays, and enlarging the area of thin-film transistors and other issues, to achieve the effects of reducing parasitic contact resistance, enhancing environmental reliability, and saving manufacturing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

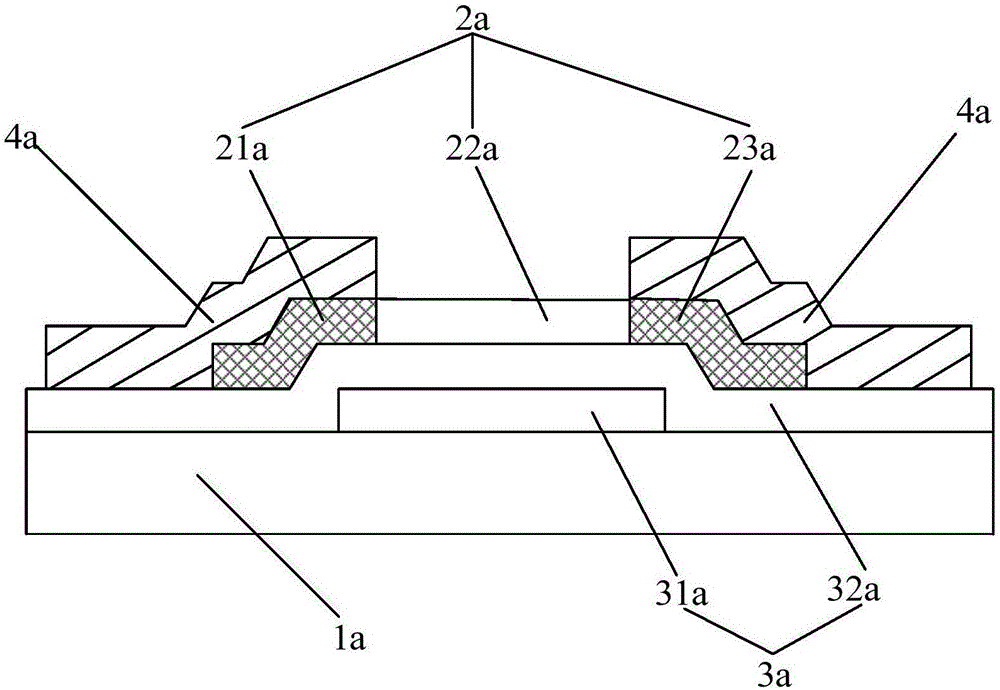

[0039] refer to figure 1 ,figure 1 It is a cross-sectional view of a back gate thin film transistor with a conventional back channel etching structure. Wherein, the thin film transistor includes: a substrate 1a, and an active layer 2a disposed on the substrate 1a. A gate stack 3a is further disposed between the active layer 2a and the substrate 1a. The gate stack 3a includes a gate electrode 31a and a gate insulating layer 32a disposed between the gate electrode 31a and the active layer 2a. The active layer 2a is covered with an electrode 4a. The area where the active layer 2a is in contact with the electrode 4a forms a source area 21a and the drain area 23a respectively, and the area where the active layer 2a is in contact with the non-electrode 4a forms a channel area 22a. Wherein, the channel region 22a is adjacent to the gate stack 3a, and the source region 21a and the drain region 23a are respectively located at two ends of the channel region 22a and connected to the c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com