Formation method of semiconductor structure

A semiconductor and gas technology, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve the problems of semiconductor structure electrical properties that need to be improved, and achieve the effects of increasing the forming process window, close contact, and reducing resistivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] It can be seen from the background art that the electrical performance of the semiconductor structure formed in the prior art needs to be improved.

[0035] In one embodiment, the forming process of the semiconductor structure includes the following steps:,

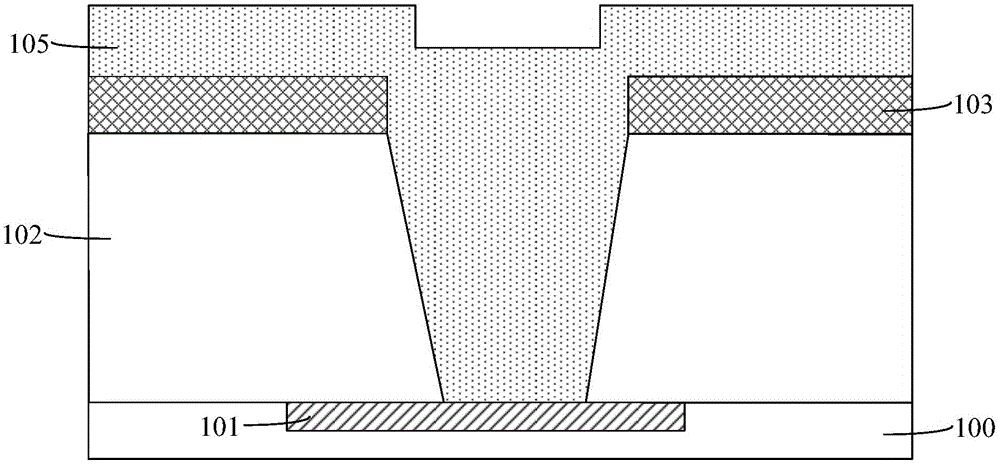

[0036] refer to figure 1 , providing a substrate 100, wherein an underlying metal layer 101 is formed in the substrate 100; a dielectric layer 102 is formed on the surface of the underlying metal layer 101 and the surface of the substrate 100; a patterned mask layer 103 is formed on the surface of the dielectric layer 102; The dielectric layer 102 is etched using the patterned mask layer 103 as a mask to form an opening 104 penetrating through the dielectric layer 102 , and the opening 104 exposes the top surface of the underlying metal layer 101 .

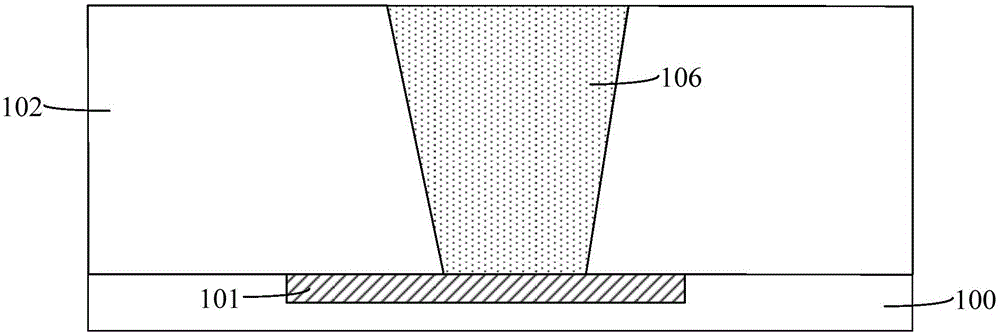

[0037] refer to figure 2 , forming to fill the opening 104 (refer to figure 1 ), and the conductive film 105 is also located on the surface of the patterned mask l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com