Chip port frequency test method

A test method and frequency technology, which is applied in the field of chip port frequency test, can solve the problems of high-efficiency mass production test, inconvenient hardware connection of external oscilloscope test, and prolonged test time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

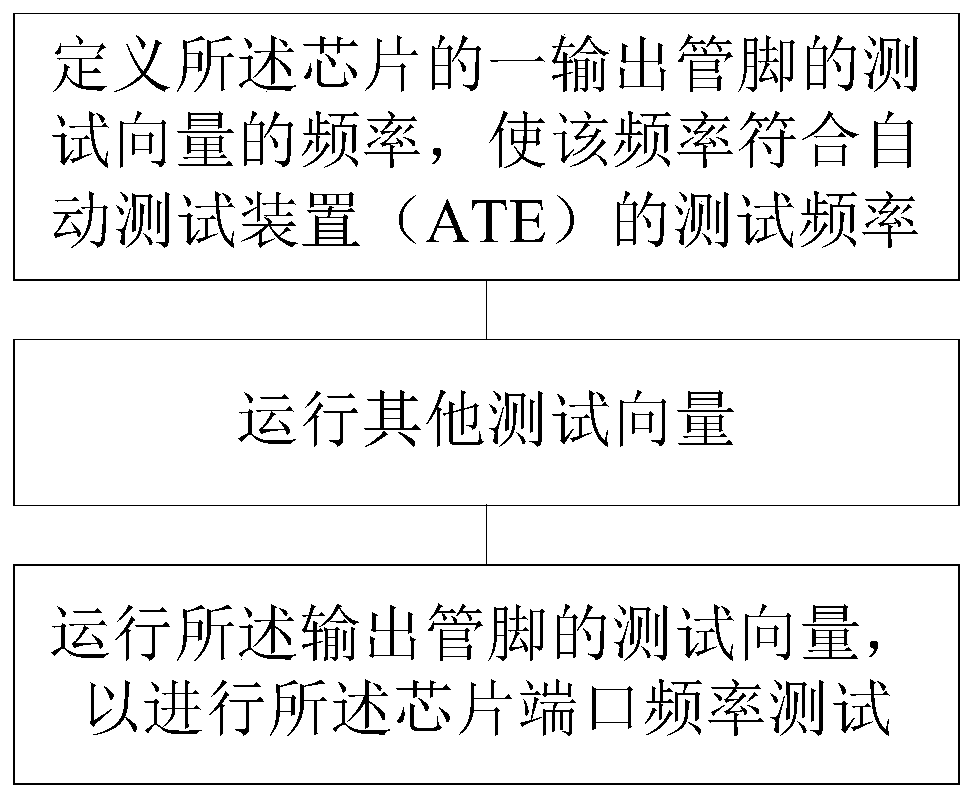

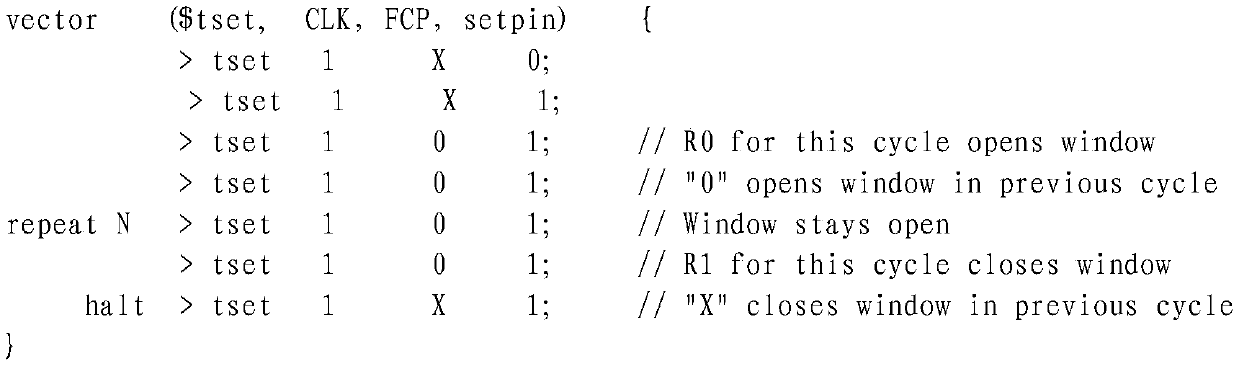

[0026] When testing the output frequency of the chip port, it is usually necessary to run the test vector first, so that the chip enters the working state required for the test. At this time, the port under test has a frequency output. Grab the signal for analysis, and obtain the output within a period of time t. The number of rising edges of the signal is n, and the output frequency of the measured port is calculated as f=n / t.

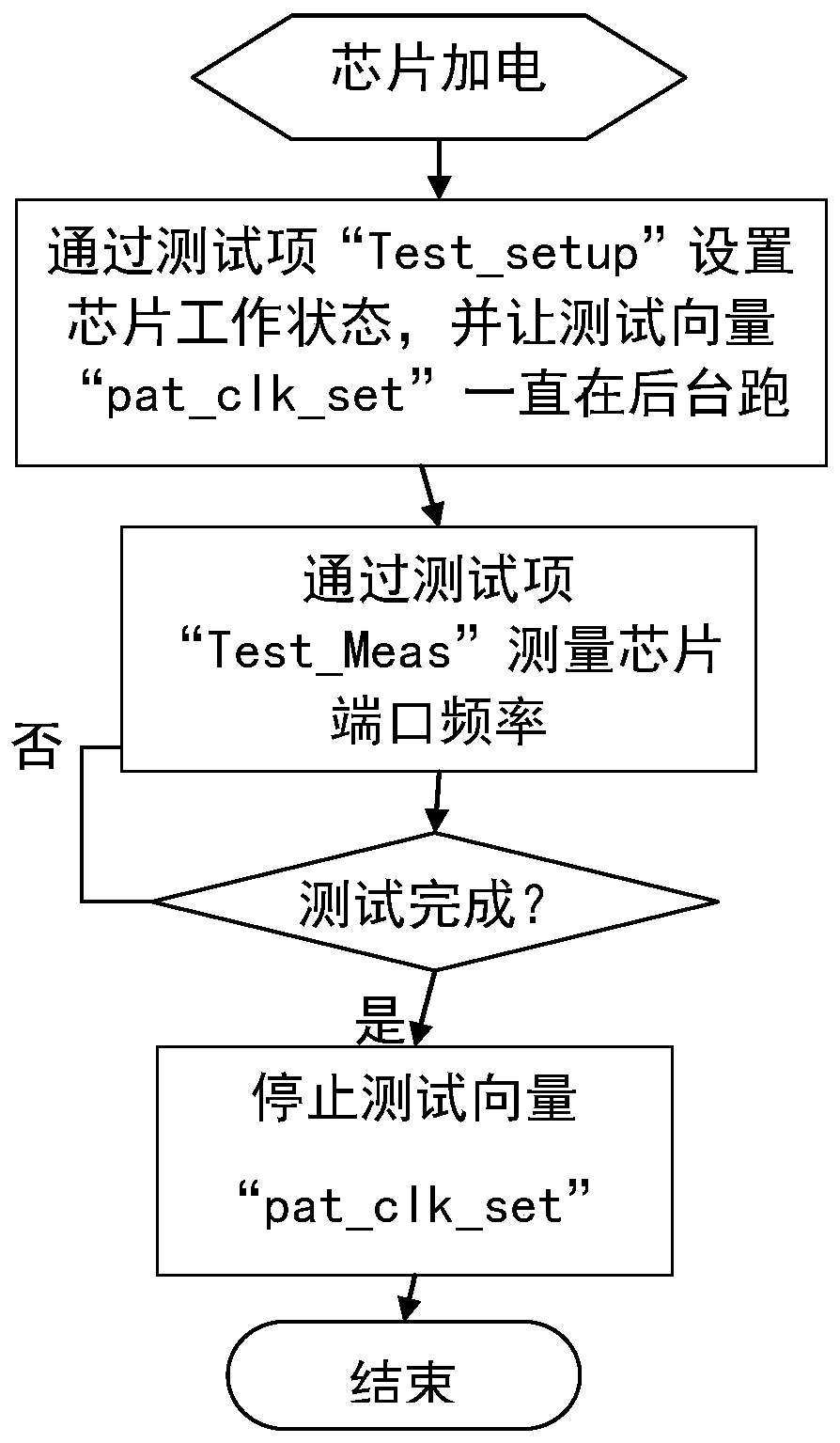

[0027] When the frequency of the test vector exceeds the highest frequency fc that the automatic test equipment (ATE) can provide in the frequency test mode, ATE does not support directly testing the port output frequency in the same test item. Such as the existing automatic test device itself supports the highest frequency of the test vector is fo = 400MHz, but only supports the highest frequency of the test vector is fc = 200MHz in the frequency test mode, now it is necessary to test the port output frequency with an expected value of 350MHz, using t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com