Reconfigurable arithmetic unit supporting multiple working modes and working modes thereof

A computing unit and working mode technology, applied in computing, computers, multi-programming devices, etc., can solve the problems of high computing efficiency, low ASIC computing efficiency, lack of versatility, etc., achieve strong flexibility, and realize computing priority The effect of management, ease of integration and use

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

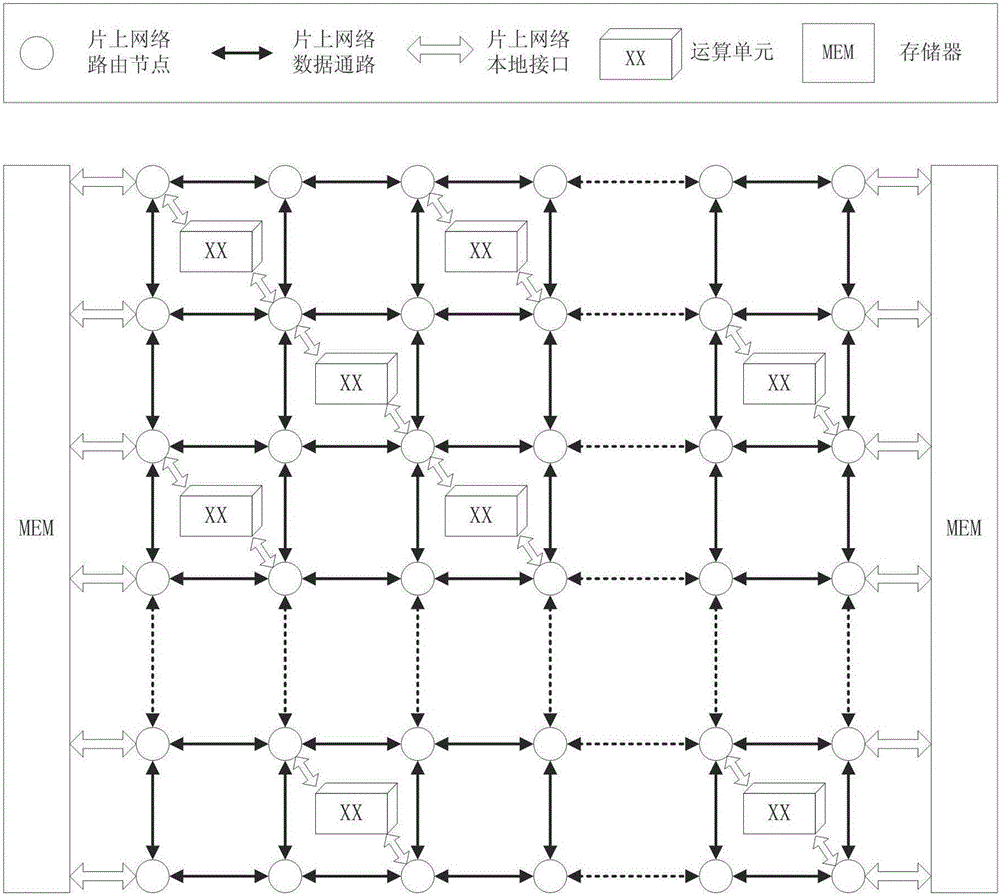

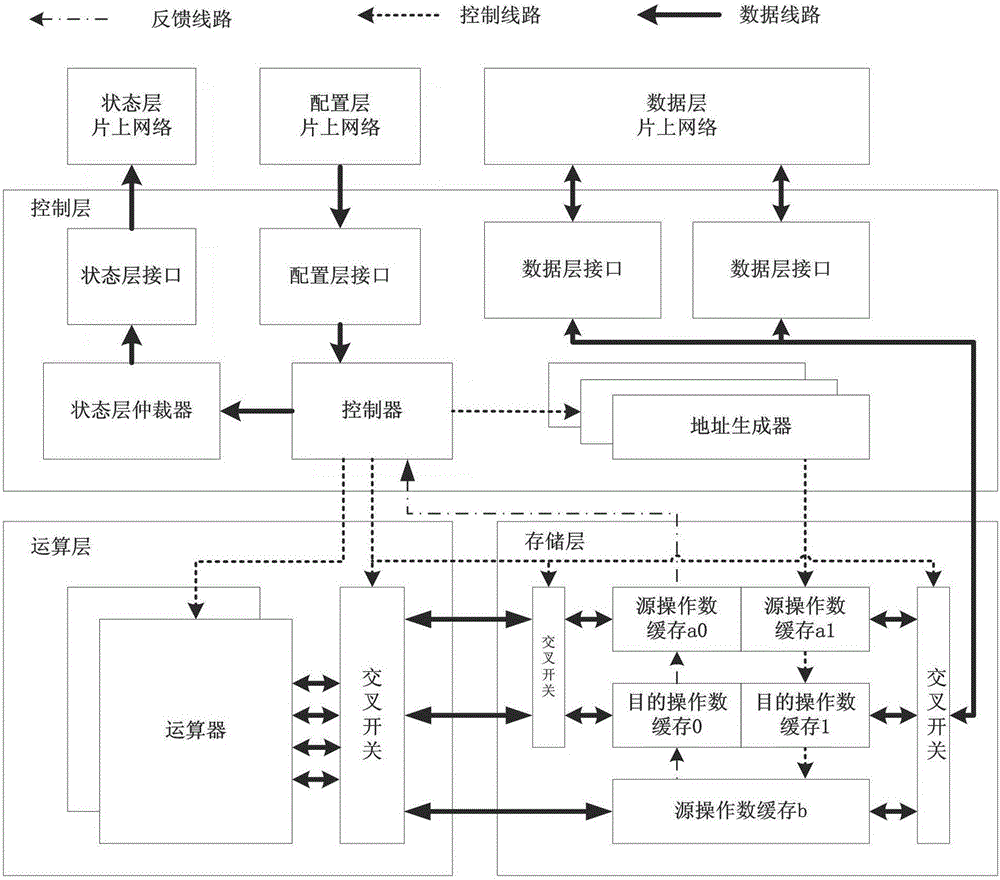

[0055] In the implementation of this example, a reconfigurable computing unit that supports multiple working modes is mounted on such as figure 1 On any two routing nodes of the on-chip network of the shown on-chip multi-core computing system, the data exchange with the on-chip network is completed through the local interface of the on-chip network; figure 2 A structural block diagram of the present invention is given, and the reconfigurable computing unit includes: a control layer, a computing layer and a storage layer;

[0056] The control layer includes: state layer interface, configuration layer interface, data layer interface, address generator and controller;

[0057] The operation layer includes: operator;

[0058] The storage layer includes: source operand cache unit, destination operand cache unit;

[0059] Both the source operand cache unit and the destination operand cache have a cache threshold. The cache threshold is based on the scale of the computing system’s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com