Semiconductor memory device

A memory and semiconductor technology, used in semiconductor devices, static memory, digital memory information, etc., can solve problems such as large standby current, latch-up, and radiation soft error.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

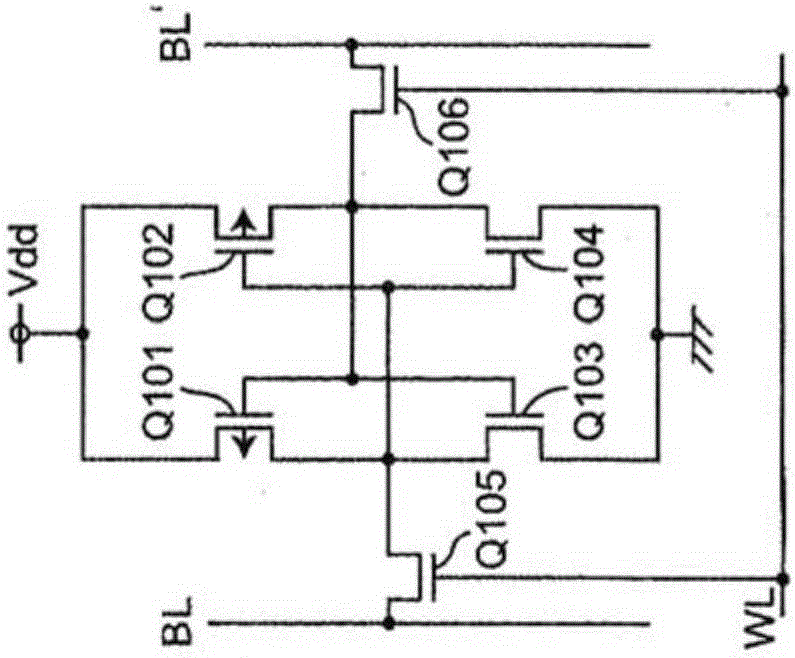

[0112] figure 2 is a circuit diagram illustrating a configuration example of a storage capacitor type SRAM related to Embodiment 1 of the present invention. image 3 is description figure 2 A longitudinal cross-sectional view of the construction of a part of a storage capacitor type SRAM.

[0113] see figure 2 , the storage capacitor type SRAM of Embodiment 1 includes 4 MOS transistors Q1T, Q2T, Q3, Q4 forming latches and 2 N-channel access transistors all located between bit lines BL, BL' and word line WL MOS transistors Q5, Q6. Here, MOS transistors Q1T, Q2T are TFT type P-channel MOS transistors and the other four MOS transistors Q3 to Q6 are embedded gate type N-channel body transistors (for example, refer to Patent Document 1). Among the semiconductor layer structures of MOS transistors, a current storage capacitor type SRAM is characterized in that an embedded gate is constituted by forming an embedded for accommodating a gate electrode and then forming a gate ele...

Embodiment 2

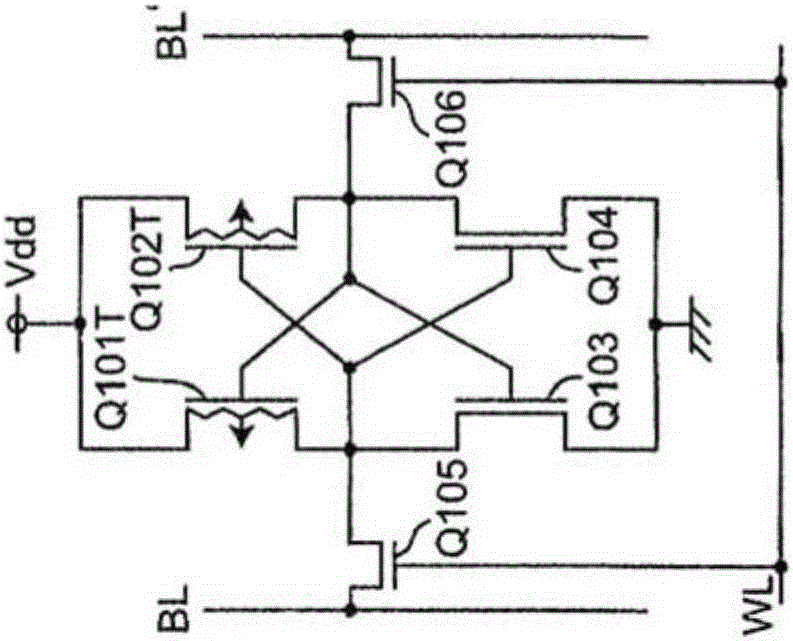

[0123] Figure 4 It is a circuit diagram illustrating a configuration example of a storage capacitor type SRAM related to Embodiment 2 of the present invention. Figure 5 is description Figure 4 A longitudinal cross-sectional view of a part of the construction of a storage capacitor type SRAM.

[0124] compare about Figure 4 The storage capacitor type SRAM in Example 2 with respect to figure 2 In the storage capacitor type SRAM of Embodiment 1, the differences are described below.

[0125] (1) TFT-type N-channel MOS transistors Q3T, Q4T are included to replace figure 2 The main body MOS transistors Q3, Q4.

[0126] (2) by having Figure 5 TFT MOS transistors Q1T, Q3T are formed by vertical integrated TFT MOS transistors Q1T, Q3T in the same gate region TG.

[0127] (3) by having Figure 5 TFT MOS transistors Q2T, Q4T are formed by vertical integrated TFT MOS transistors Q2T, Q4T in the same gate region TG.

[0128] exist Figure 5Among them, MOS transistors Q1T, ...

Embodiment 3

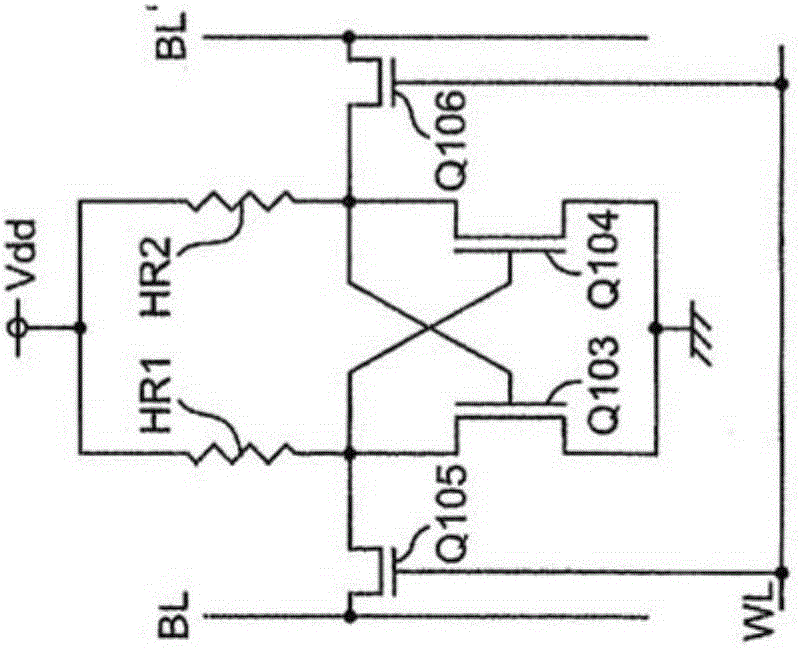

[0141] Image 6 It is a circuit diagram illustrating a configuration example of a storage capacitor type SRAM related to Embodiment 3 of the present invention. Figure 7 are instructions for Image 6 A longitudinal sectional view of the structure of the silicon-on-insulator (SOI) type access MOS transistors Q5L, Q6L in the storage capacitor type SRAM of .

[0142] compare about Image 6 The storage capacitor type SRAM in Example 3 with respect to figure 2 In the storage capacitor type SRAM of Embodiment 1, differences are described as follows.

[0143] (1) A body leakage MOS transistor Q5L having a back gate control terminal LT is included instead of the access MOS transistor Q5.

[0144] (2) A capacitor C3 is included instead of the MOS transistor Q3, wherein one end of the capacitor C3 is connected to the node P2 and the other end of the capacitor C3 is connected to the back gate control terminal LT of the leaky MOS transistor Q5L.

[0145] (3) A body leakage MOS trans...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com