Method for improving selected area epitaxial growth interface

A technology of selective area epitaxy and interface, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., to achieve the effect of improving crystal quality and low dislocation density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0036] Such as Picture 8 Shown here is a schematic diagram of the selected region epitaxial structure of this embodiment. The structure includes a substrate (1), a stress buffer layer (2), a GaN buffer layer (3), a GaN insertion layer (4), and a GaN trench from bottom to top. Road layer (5), AlGaN barrier layer (6). The manufacturing method of the above-mentioned selective area epitaxial structure is as Figure 1-Figure 8 As shown, including the following steps:

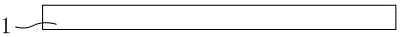

[0037] 1) Provide a substrate (1); such as figure 1 Shown.

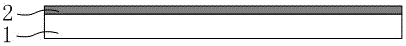

[0038] 2) Growing a stress buffer layer (2) on the substrate (1); such as figure 2 Shown.

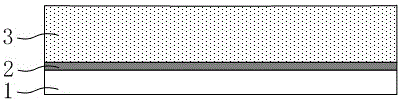

[0039] 3) Grow a GaN buffer layer (3) on the stress buffer layer; image 3 Shown.

[0040] 4) Deposit a layer of SiO2 on the GaN buffer layer (3) as a mask layer (7);. Such as Figure 4 Shown.

[0041] 5) Use photolithography and development technology and wet etching to remove the dielectric layer in the area where the epitaxial AlGaN is needed to realize the patterning...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com