Semiconductor device forming method

A semiconductor and device technology, applied in the field of semiconductor device formation, can solve the problems of low electrical performance of semiconductor devices and large loss of interlayer dielectric layers, etc., and achieve excellent electrical performance, low etching rate, and reduced etching Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

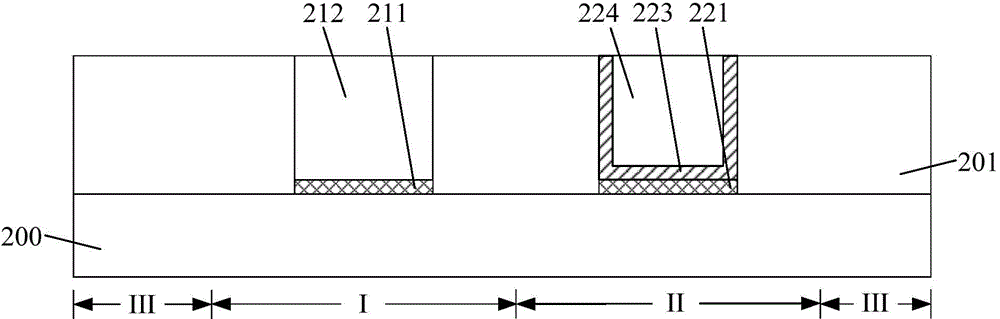

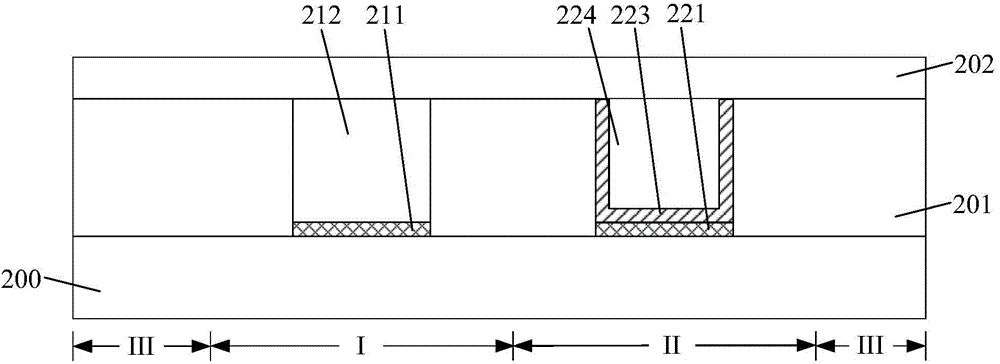

[0031] It can be seen from the background art that the electrical performance of semiconductor devices formed in the prior art needs to be improved.

[0032]It has been found through research that in order to meet the requirements of improving the threshold voltage (ThresholdVoltage) of NMOS tubes and PMOS tubes at the same time, different metal materials are usually used as the work function (WF, WorkFunction) layer materials of the metal gates of NMOS tubes and PMOS tubes, so NMOS tubes The metal gates of the transistor and the PMOS transistor are formed successively. In one embodiment, a method for forming a semiconductor device includes the following steps:

[0033] Step S1, providing a substrate including an NMOS region and a PMOS region, a first dummy gate is formed on a part of the substrate of the NMOS region, a second dummy gate is formed on a part of the substrate of the PMOS region, and an interlayer is formed on the surface of the substrate A dielectric layer, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com