A Glitch-Free Switching Circuit Supporting Multiple Clocks

A switching circuit, glitch-free technology, applied in the direction of electrical components, pulse processing, pulse technology, etc., can solve the problems of not supporting multi-channel clock jumping glitch-free switching, not supporting jumping clock switching, etc., to ensure uniqueness and exclusivity, avoiding illegal switching, and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

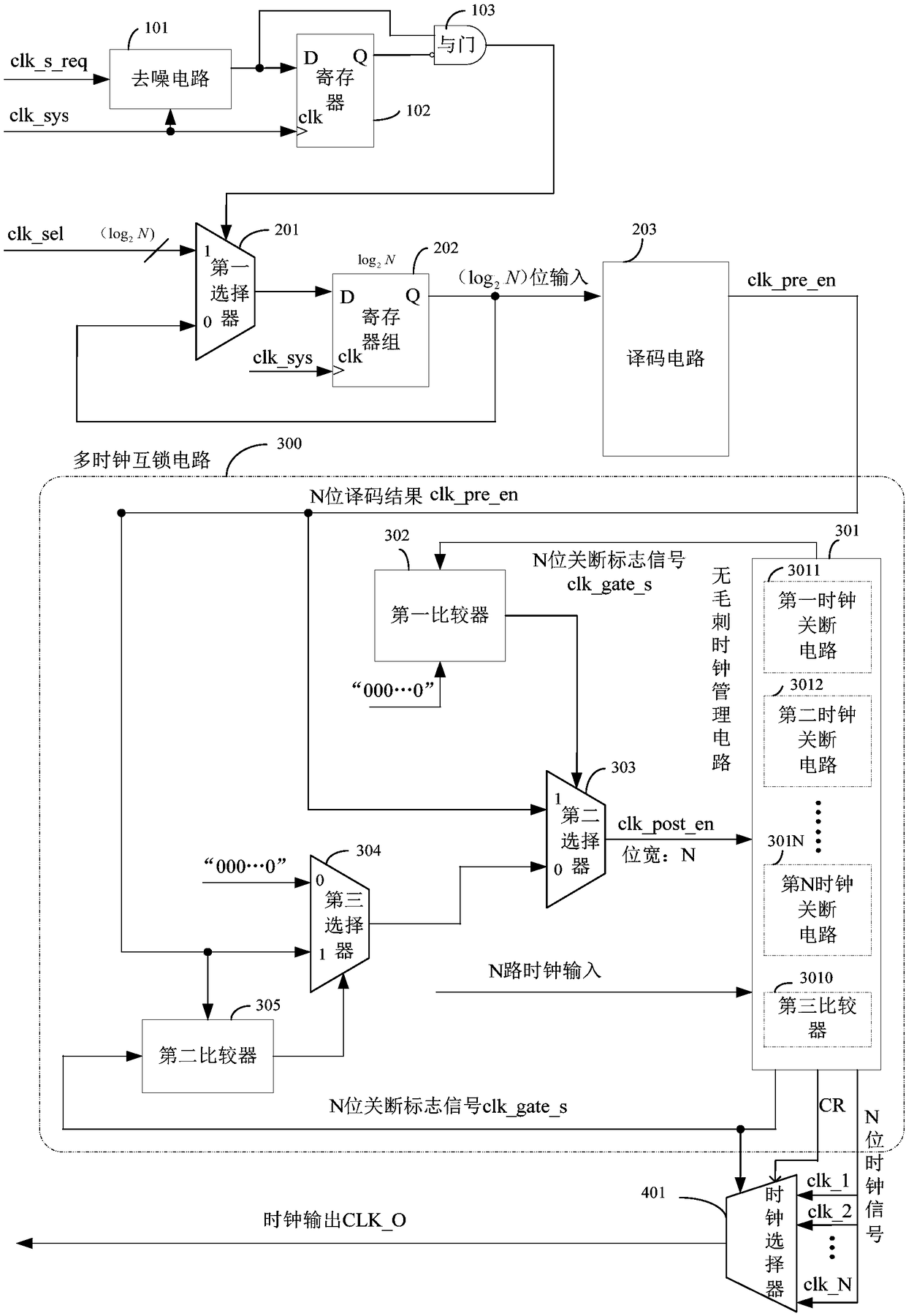

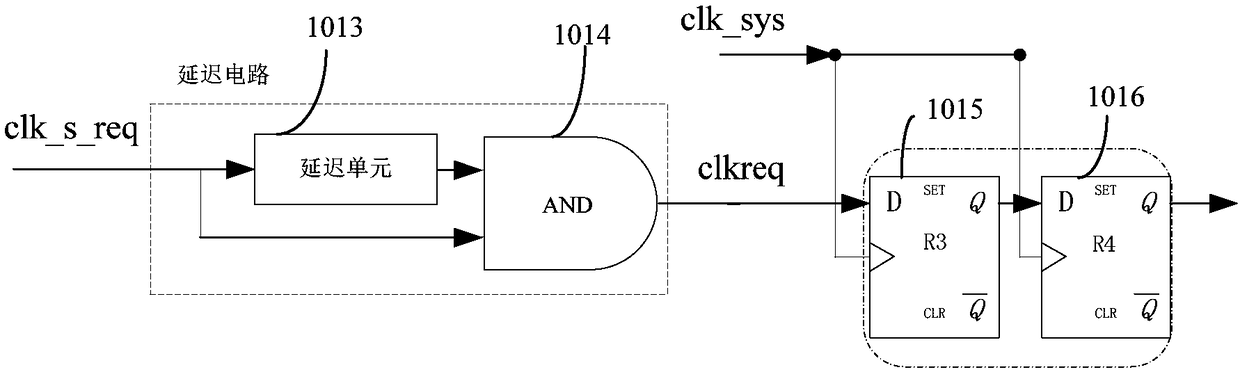

[0024] A glitch-free switching circuit supporting multiple clocks in the present invention first performs denoising processing on the clock switching request, then saves the clock selection signal based on the effective clock switching request, and performs independent based on the saved clock selection signal For hot code decoding, only one bit of the decoding result is high level, and then the multi-clock interlock circuit will process the decoding result according to the current output clock enable (marking the current output clock), if the current output When the clock enable is zero, the decoding result is directly passed to the input of the clock management circuit; if the current output clock enable is non-zero, the decoding result is compared with the current output clock enable, and i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com