Method for forming fin type field effect transistor

A fin field effect and transistor technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems that the electrical parameters of the fin field effect transistor cannot meet the requirements, and it is difficult to accurately control the thickness of the gate dielectric layer. , to achieve the effect of easy thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

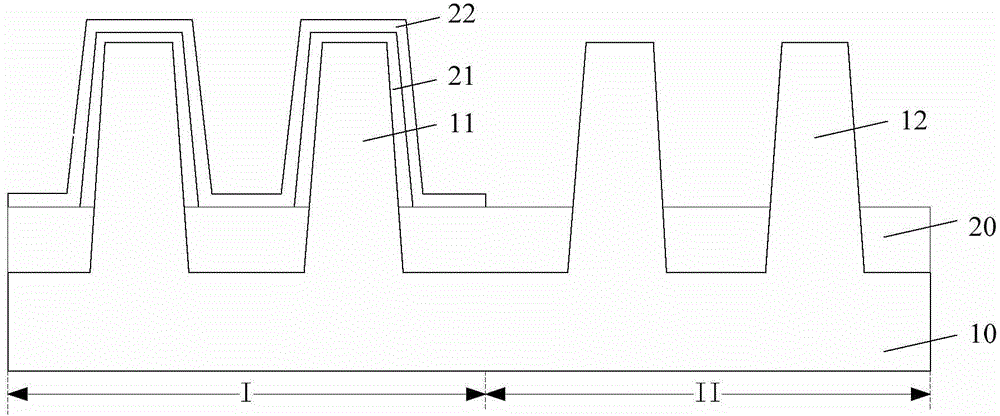

[0031] As mentioned in the background art, in the prior art, when transistors in the core region and the peripheral region are formed at the same time, it is difficult to accurately control the gate dielectric layer of the transistor in the peripheral region, which easily leads to unsatisfactory device performance.

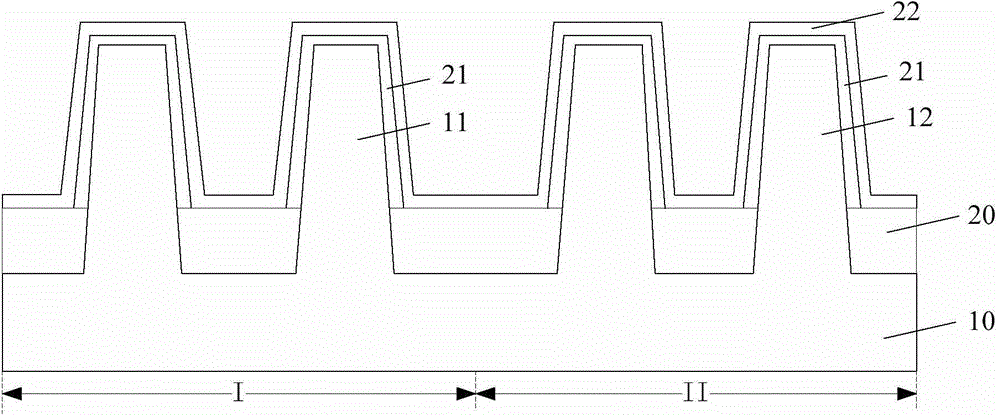

[0032] Figure 1 to Figure 4 A formation process of a gate dielectric layer of a fin field effect transistor according to an embodiment is provided.

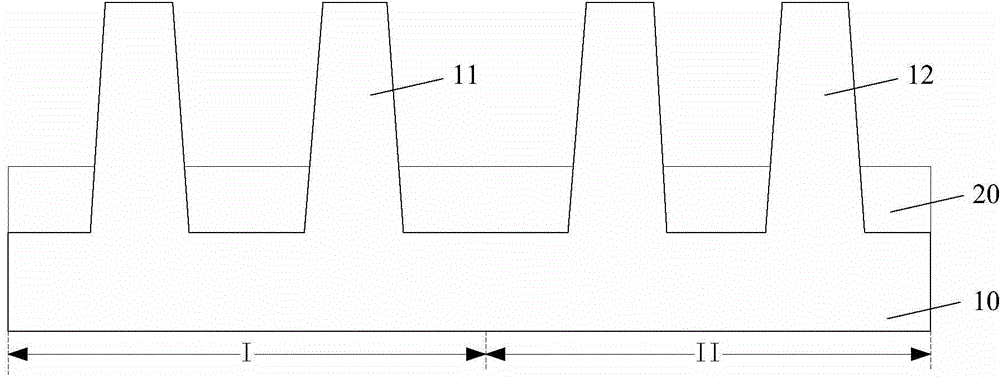

[0033] Please refer to figure 1 , provide a semiconductor substrate 10, the semiconductor substrate 10 includes a first region I and a second region II, a first fin 11 is formed on the first region I, and a second fin is formed on the second region II. Fin 12 , a dielectric layer 20 is formed on the surface of the semiconductor substrate 10 , and the surface of the dielectric layer 20 is lower than the surfaces of the first fin 11 and the second fin 12 .

[0034] The first region I is used to form peripheral circu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com