Rapidly-adaptive all-digital phase-locked loop and design method thereof

An all-digital phase-locked loop, self-adaptive technology, applied in the field of electronics, can solve the problems of increasing phase jitter, compromise, system stability deterioration, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The technical solution of the present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

[0031] 1. Design of digital phase detector

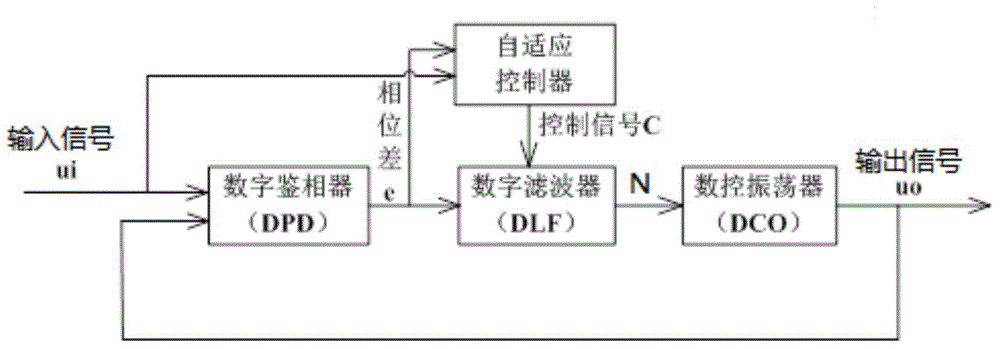

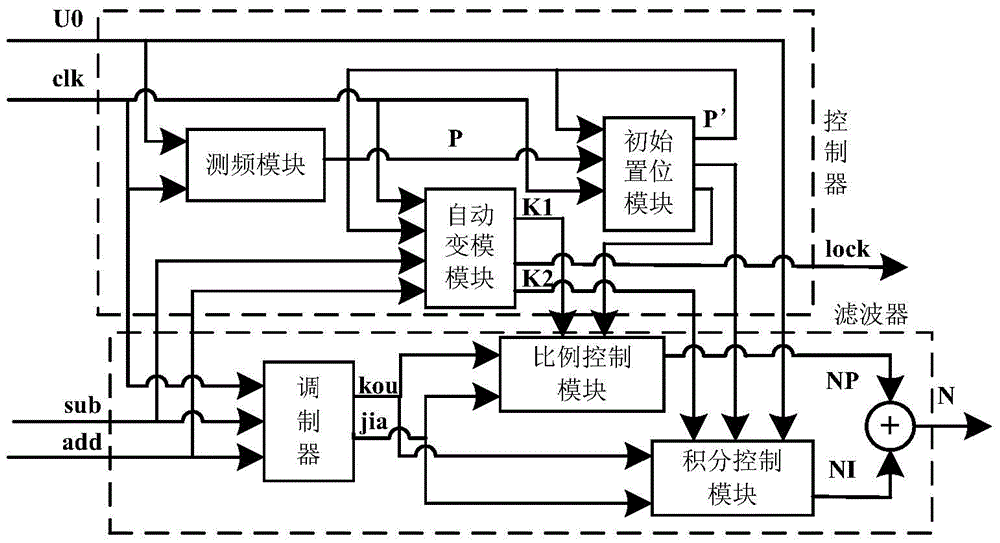

[0032] figure 1 It is a schematic diagram of the structure of a fast adaptive all-digital phase-locked loop. An adaptive controller is added to the all-digital phase-locked loop, and the circuit structure of the digital phase detector and digital filter is improved, so that the phase-locked loop can dynamically adjust By adjusting the control parameters, the phase-locking speed is improved, the phase-locking range is expanded, and the stability of the phase-locking system is enhanced. It overcomes the defects caused by the fixed and non-dynamic adjustment of the traditional all-digital phase-locked loop control parameters.

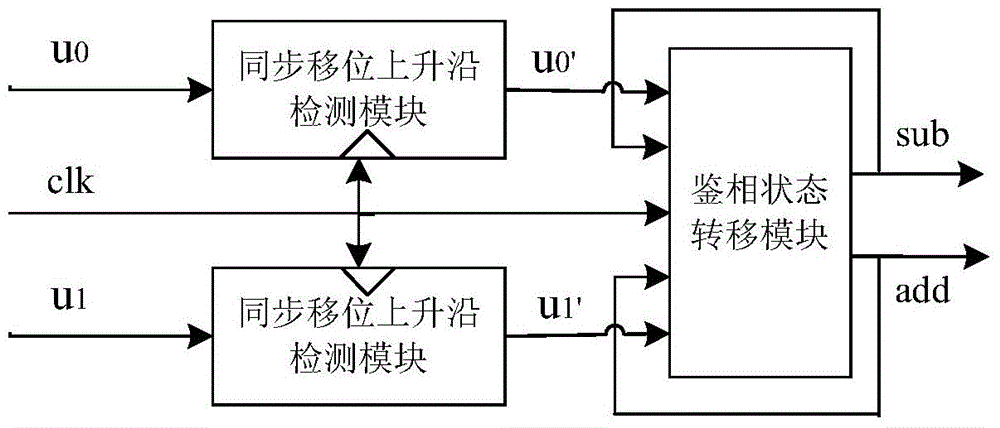

[0033] figure 2 It is the structure diagram of the digital phase detector. It consists of two synchronous shift rising edge detection mo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com