Logic delay locking based anti-interference circuit and method

A logic delay and delay circuit technology, applied in the direction of single output arrangement, etc., can solve the problems of time jitter, affecting the quality of trigger signals, and electronic equipment cannot be accurately triggered, so as to achieve the effect of suppressing signal interference signals

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

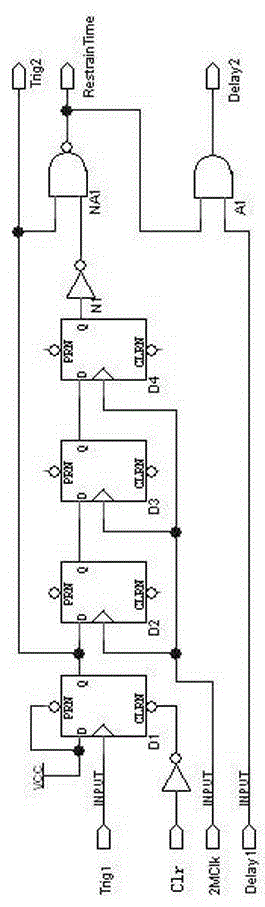

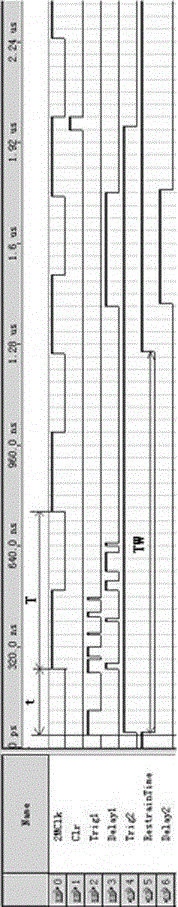

[0039] Embodiment 1: as figure 1 shown. The circuit includes 4 D flip-flops (where D1 is used as a step signal generator, and the delay circuit includes flip-flop D2, flip-flop D3, and flip-flop D4), 2 inverters, 1 NAND gate and 1 AND gate . The trigger signal Trig1 is connected to the clock input terminal of the trigger D1, the output terminal of the trigger D1 is connected to the signal input terminal of the trigger D2, the output terminal of the trigger D2 is connected to the signal input terminal of the trigger D3, and the output terminal of the trigger D3 is connected to the signal input terminal of the trigger D4 The signal input terminals are connected, and the clock signal 2MClk is connected with the clock input terminals of flip-flops D2-D4 at the same time. The output terminal of the trigger D4 is connected to the input terminal of the inverter N1, the output terminal of the inverter N1 is connected to one input terminal of the NAND gate NA1, the output terminal of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com