Chip and forming method, packaged product, method for improving yield rate of packaged product

A technology for chips and finished products, which is applied in the field of chips, forming methods, and packaged finished products. It can solve problems such as chip performance not meeting design requirements, yield reduction, chip failure, etc., and achieve good interconnection performance and chip packaging product yield. high effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

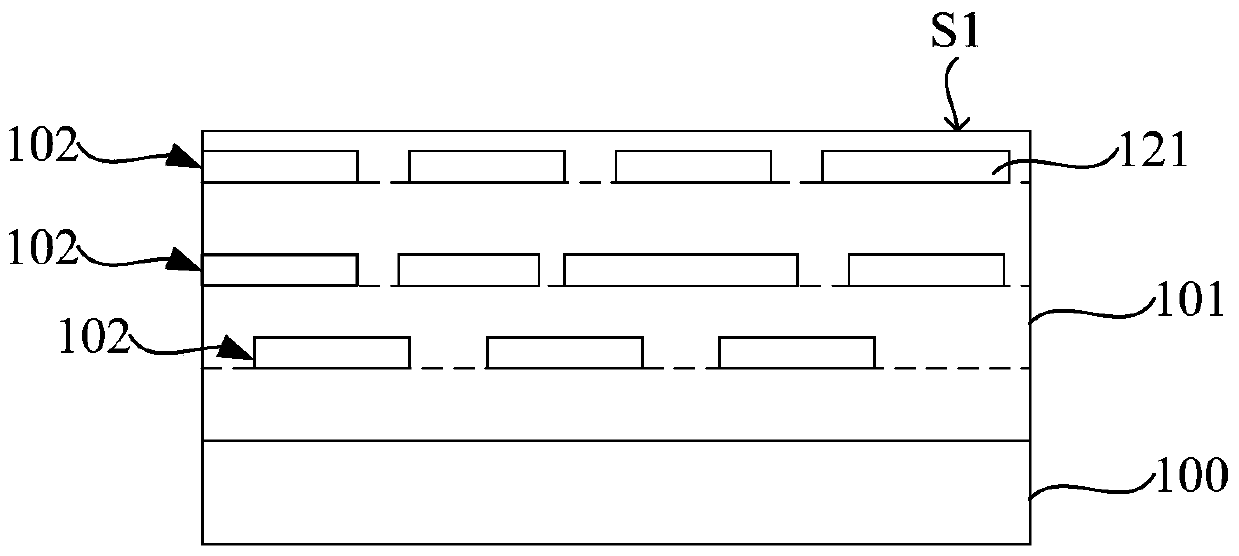

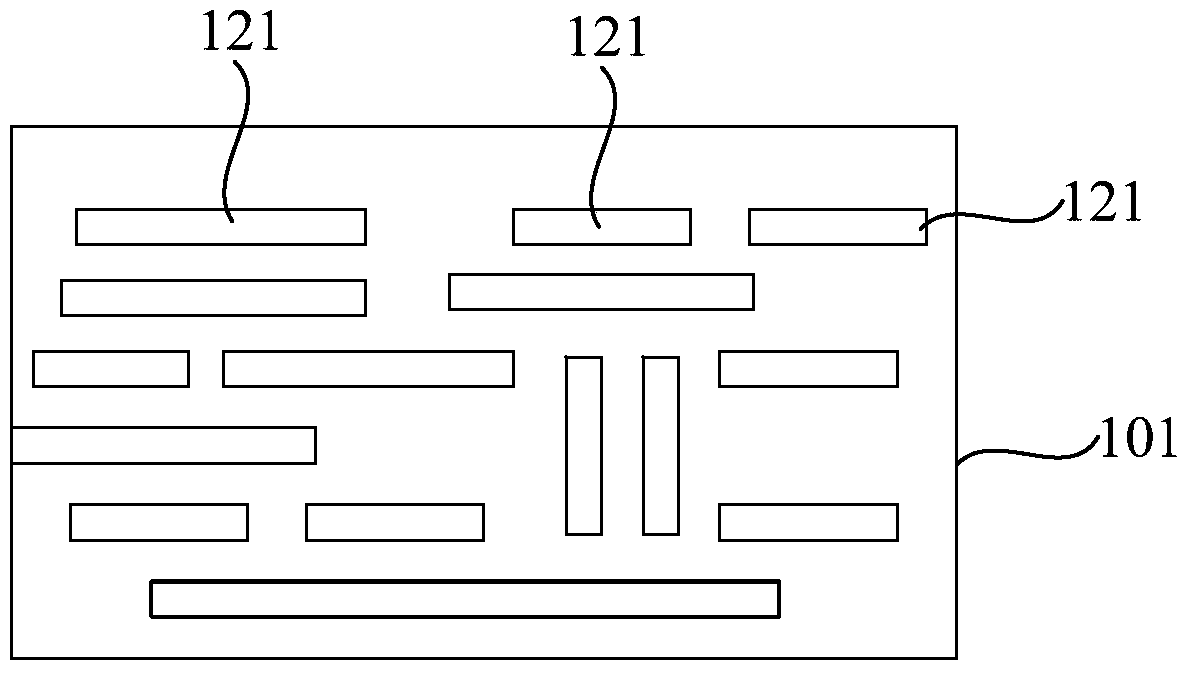

[0042] Aiming at the problems existing in the prior art, the inventor conducted a statistical analysis and found that: in the direction perpendicular to the front of the chip, among the two interconnected metal layers on both sides of the interlayer dielectric material layer where the fracture occurred, one or both The metal density of the layer interconnect metal layer is relatively small, less than about 0.3. The metal density refers to the ratio of the projected surface area of a layer of interconnection metal layer directly below the copper pillar bump on the front surface of the chip to the surface area occupied by the copper pillar bump on the front surface of the chip. When the metal density of a layer of interconnect metal layer under the copper pillar bump is less than 0.3, the mechanical strength of the interlayer dielectric material layer on both sides of the interconnect metal layer perpendicular to the direction of the front of the chip is insufficient. , It is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com