Isolation N-type laterally diffused metal oxide semiconductor (NLDMOS) device and manufacturing method thereof

A manufacturing method and isolation technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of depletion of accelerated drift region, increase of device on-resistance, etc., to increase effective doping concentration, conduction The effect of reducing the on-resistance and increasing the current channel

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

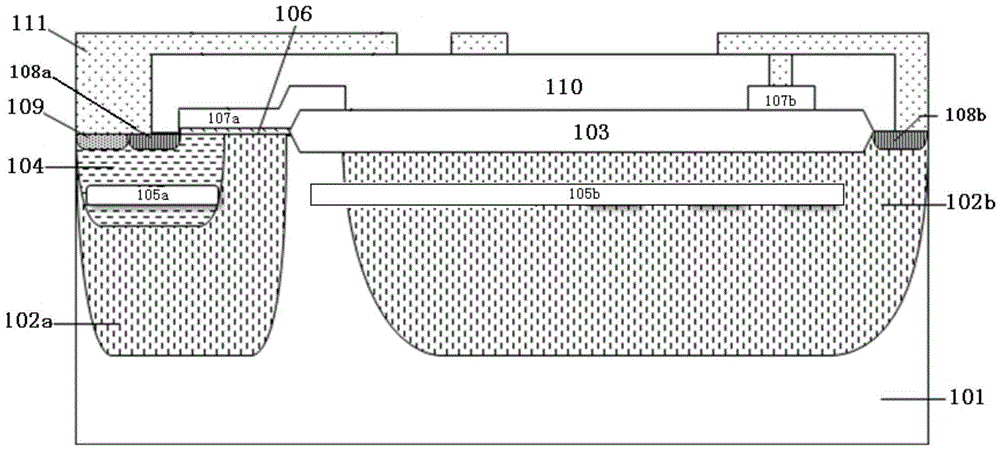

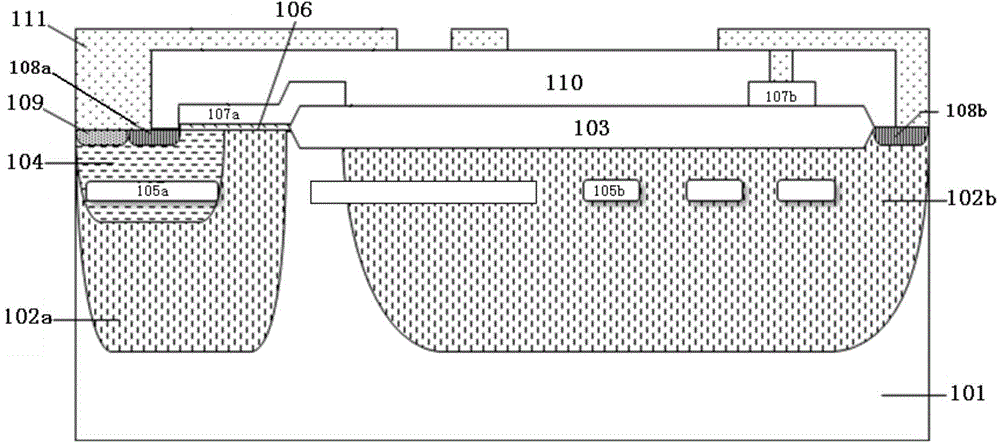

[0050] Isolated NLDMOS device, cell structure such as figure 2 As shown, two independent N-type deep wells, a left N-type deep well 102a and a right N-type deep well 102b, are formed on the P-type silicon substrate 101;

[0051] The left N-type deep well 102a has a P well 104 formed on the left;

[0052] In the P well 104, a P-type heavily doped region 109 and a source N-type heavily doped region 108a are formed on the left;

[0053]A gate oxide layer 106 is formed above the right part of the P well 104 and above the right part of the left N-type deep well 102a;

[0054] Field oxygen 103 is formed above the P-type silicon substrate 101 between the left N-type deep well 102a and the right N-type deep well 102b, and above the left part of the right N-type deep well 102b;

[0055] The right N-type deep well 102b has a drain N-type heavily doped region 108b formed on the right;

[0056] A gate polysilicon 107a is formed above the left part of the field oxygen 103 and above the...

Embodiment 2

[0069] The manufacturing method of the isolated NLDMOS device of Embodiment 1 includes the following process steps:

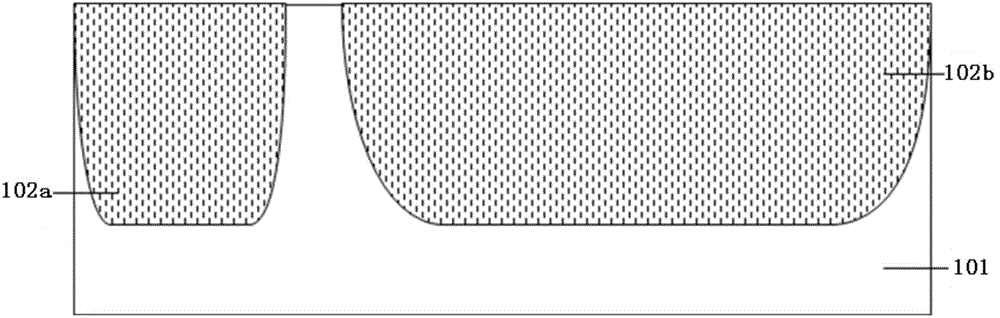

[0070] 1. On the P-type silicon substrate 101, two independent N-type deep wells, the left N-type deep well 102a and the right N-type deep well 102b, are formed by N-type ion implantation, as image 3 shown;

[0071] 2. Open the field oxygen region by using active region lithography, etch the field oxygen region above the P-type silicon substrate 101 between the left N-type deep well 102a and the right N-type deep well 102b, and the right N-type deep well 102b above the left part, growth field oxygen 103, such as Figure 4 shown;

[0072] 3. Photolithography opens the well implantation region, and implants P-type impurity ions into the left part of the left N-type deep well 102a to form a P well 104, such as Figure 5 As shown, the P well 104 serves as the background region of the isolated NLDMOS device;

[0073] Four. Carry out P-type ion implantation belo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com