Array substrate and preparation method thereof

A technology for array substrates and capacitor areas, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems that cannot meet design requirements, and achieve the goals of avoiding high deviation, reducing wiring space, and increasing capacitance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

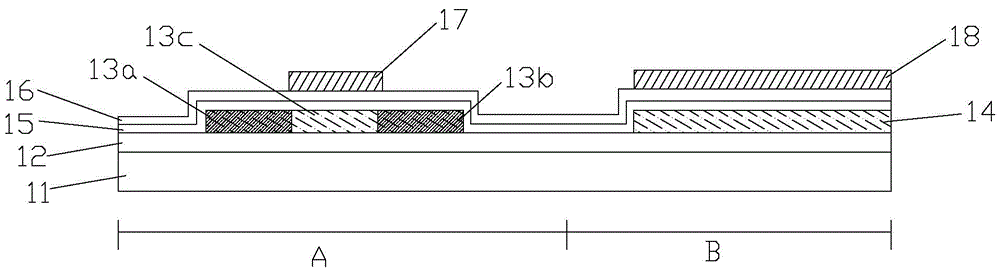

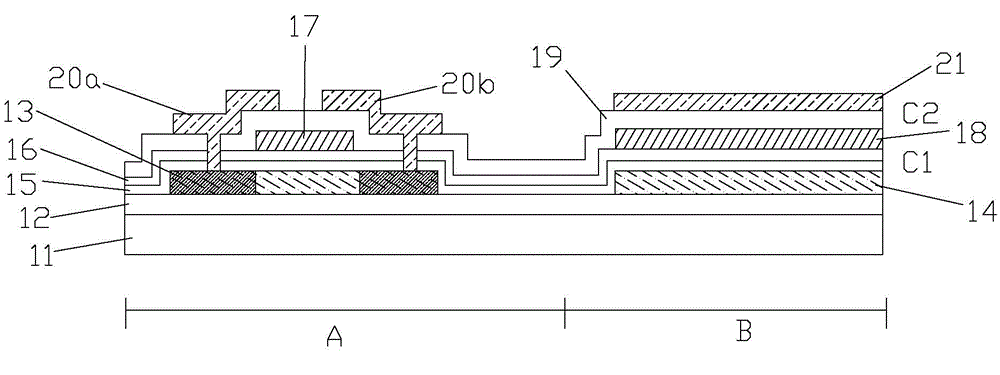

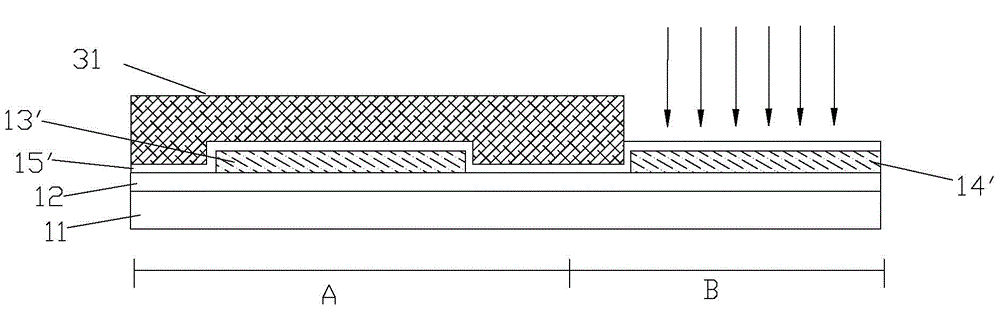

[0067] Figure 3A , 3B , 3C are cross-sectional views of pixels corresponding to the preparation method of etching away the first gate insulating layer by one-time exposure.

[0068] 1) if Figure 3A As shown, a buffer layer 12 covering the thin film transistor region A and the capacitor region B of the substrate is formed on the substrate 11, and the buffer layer 12 can be made of silicon dioxide (SiO 2 ) layer, and can also be formed by a double-layer buffer layer of silicon dioxide and silicon nitride (SiNx).

[0069] 2) An amorphous silicon layer is deposited on the buffer layer 12, and the amorphous silicon layer is crystallized to form a polysilicon layer, and photolithography is used to form the polysilicon layer corresponding to the thin film transistor above the thin film transistor region and the polysilicon layer corresponding to the capacitor above the capacitor region , and then P - Ion doping forms the thin film transistor semiconductor layer 13' and the capa...

Embodiment 2

[0077] Figure 4A , Figure 4B Shown is a cross-sectional view of a pixel corresponding to the preparation method of etching away the first gate insulating layer by adopting a double exposure method. The preparation method is basically the same as that in Example 1, the difference is: step 3) coating photoresist on the semiconductor pattern layer, and then using a capacitively doped photomask to expose and develop, so that the photoresist in the thin film transistor region remains. Form the photoresist layer 41, the photoresist layer 41 covers the area except the capacitor semiconductor layer 14', and the capacitor semiconductor layer 14' is photoresisted. + Ion doping forms the first electrode 14; after peeling off the photoresist layer 41, an insulating layer 15' is formed on the semiconductor pattern layer, corresponding to the thin film transistor region and capacitor region covering the substrate, and then the insulating layer 15' is coated with photoresist , using the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com