Optimization method of microprocessor microarchitecture parameters based on simulator

A technology of microprocessor and architecture, applied in the fields of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of long time consumption, long time consumption, coarse granularity of performance statistics, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

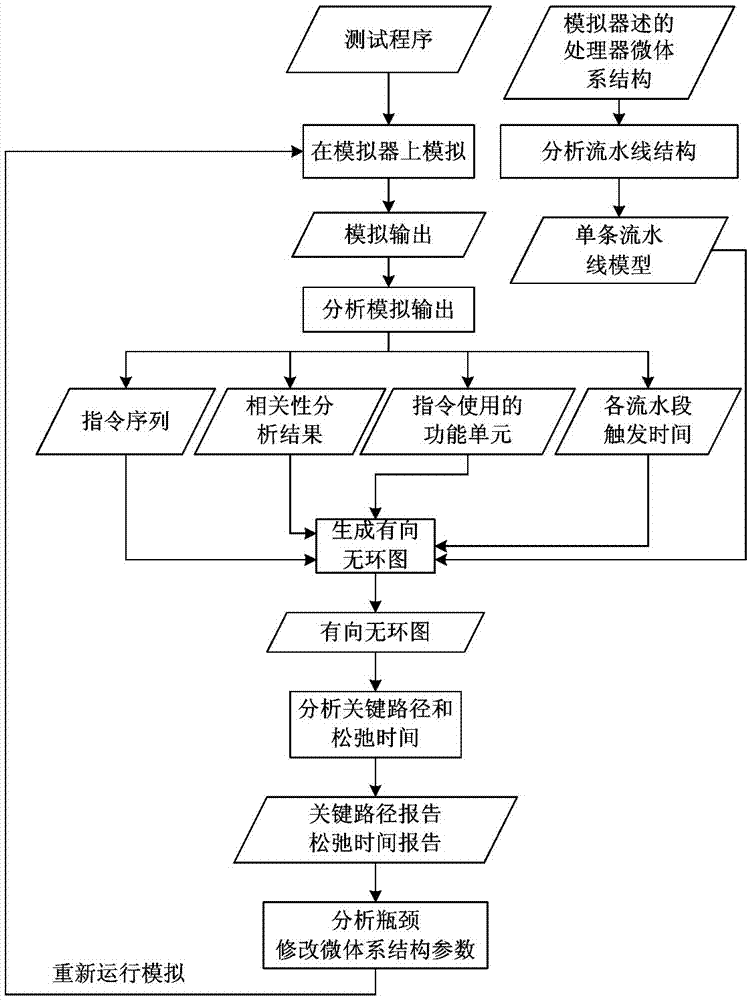

[0069] Such as figure 1 As shown, the implementation steps of the emulator-based microprocessor microarchitecture parameter optimization method in this embodiment are as follows:

[0070] 1) Analyze the processor microarchitecture described by the clock-accurate simulator, and construct the pipeline model of the microprocessor.

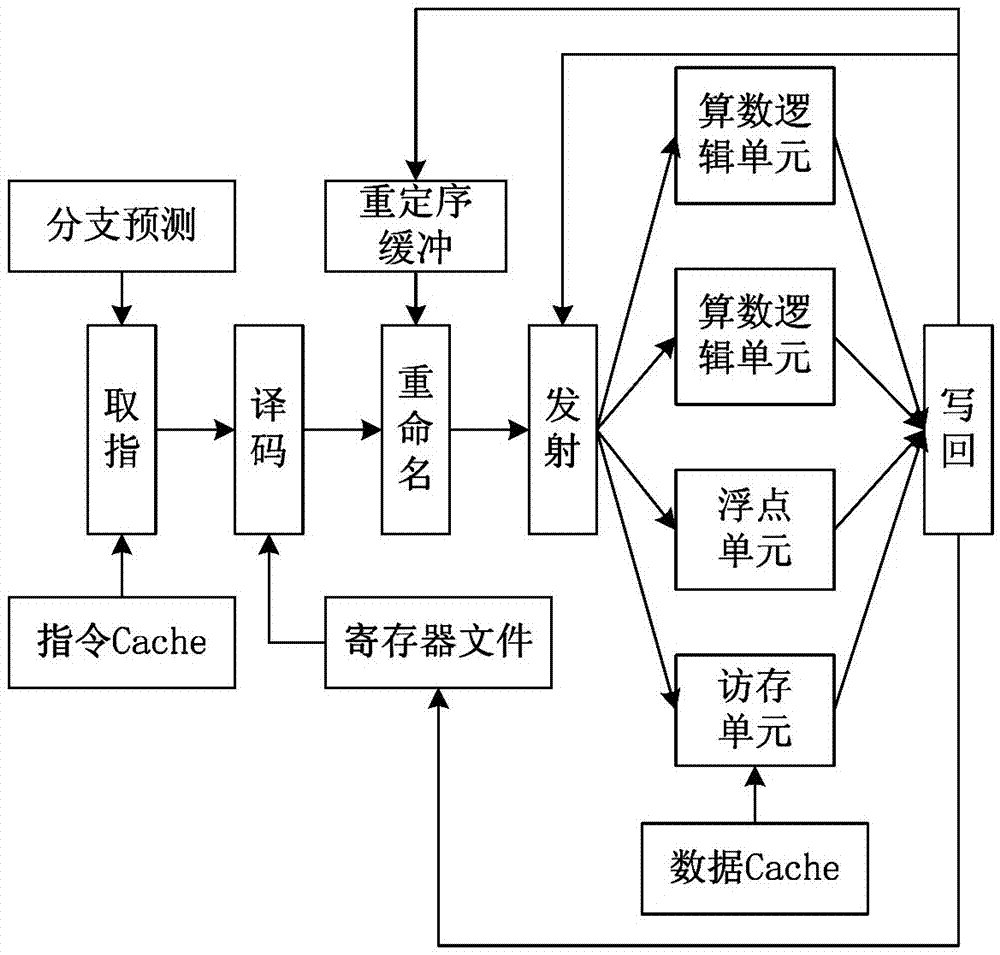

[0071] see figure 2 The microarchitecture of the superscalar out-of-order pipeline shown, the pipeline includes 6 pipeline segments, namely fetch, decode, rename, issue, and execute And write back (commit), where the execution (exe) includes 2 arithmetic logic units (ALU), 1 floating point unit (FP), and 1 memory access unit (load / store). The instruction fetch segment needs to access the instruction cache, and the memory segment needs to access the data cache. To rename a segment, you need to apply for a rename buffer. The decode segment needs to read the register file. The result of the branch prediction will affect the instruction fetch. The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com